Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>OCP</strong>-<strong>IP</strong> Confidential<br />

exist, C-TRIG will connect to 42 signals (7x2x3). In this case TAP doesn't mean JTAG<br />

programming. The programming model could be memory mapped and still support the<br />

described C-TRIG interface. This is one more advantage of mapping the hardware to the <strong>OCP</strong><br />

fabric.<br />

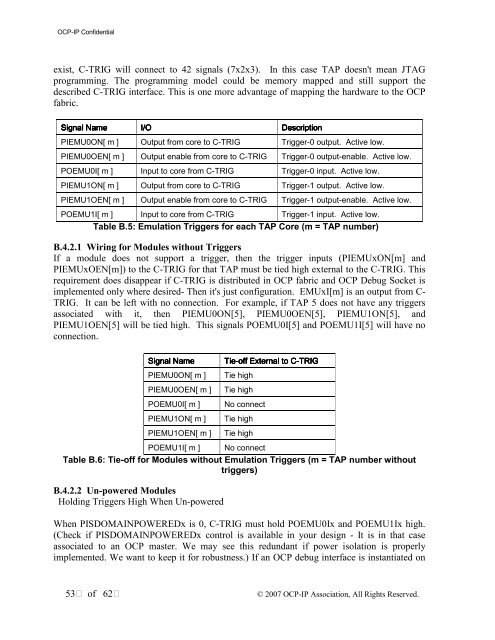

Signal Name<br />

I/O<br />

Description<br />

PIEMU0ON[ m ] Output from core to C-TRIG Trigger-0 output. Active low.<br />

PIEMU0OEN[ m ] Output enable from core to C-TRIG Trigger-0 output-enable. Active low.<br />

POEMU0I[ m ] Input to core from C-TRIG Trigger-0 input. Active low.<br />

PIEMU1ON[ m ] Output from core to C-TRIG Trigger-1 output. Active low.<br />

PIEMU1OEN[ m ] Output enable from core to C-TRIG Trigger-1 output-enable. Active low.<br />

POEMU1I[ m ] Input to core from C-TRIG Trigger-1 input. Active low.<br />

Table B.5: Emulation Triggers for each TAP <strong>Core</strong> (m = TAP number)<br />

B.4.2.1 Wiring for Modules without Triggers<br />

If a module does not support a trigger, then the trigger inputs (PIEMUxON[m] and<br />

PIEMUxOEN[m]) to the C-TRIG for that TAP must be tied high external to the C-TRIG. This<br />

requirement does disappear if C-TRIG is distributed in <strong>OCP</strong> fabric and <strong>OCP</strong> <strong>Debug</strong> Socket is<br />

implemented only where desired- Then it's just configuration. EMUxI[m] is an output from C-<br />

TRIG. It can be left with no connection. For example, if TAP 5 does not have any triggers<br />

associated with it, then PIEMU0ON[5], PIEMU0OEN[5], PIEMU1ON[5], and<br />

PIEMU1OEN[5] will be tied high. This signals POEMU0I[5] and POEMU1I[5] will have no<br />

connection.<br />

Signal Name<br />

PIEMU0ON[ m ]<br />

PIEMU0OEN[ m ]<br />

POEMU0I[ m ]<br />

PIEMU1ON[ m ]<br />

PIEMU1OEN[ m ]<br />

POEMU1I[ m ] No connect<br />

Table B.6: Tie-off for Modules without Emulation Triggers (m = TAP number without<br />

triggers)<br />

B.4.2.2 Un-powered Modules<br />

Holding Triggers High When Un-powered<br />

Tie-off External to C-TRIG<br />

C<br />

Tie high<br />

Tie high<br />

No connect<br />

Tie high<br />

Tie high<br />

When PISDOMAINPOWEREDx is 0, C-TRIG must hold POEMU0Ix and POEMU1Ix high.<br />

(Check if PISDOMAINPOWEREDx control is available in your design - It is in that case<br />

associated to an <strong>OCP</strong> master. We may see this redundant if power isolation is properly<br />

implemented. We want to keep it for robustness.) If an <strong>OCP</strong> debug interface is instantiated on<br />

53 of 62<br />

© 2007 <strong>OCP</strong>-<strong>IP</strong> Association, All Rights Reserved.