Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>OCP</strong>-<strong>IP</strong> Confidential<br />

number. This will be 0 or 1, depending on the trigger that is in question. If any one or more of<br />

these conditions is true, then the trigger should be 0.<br />

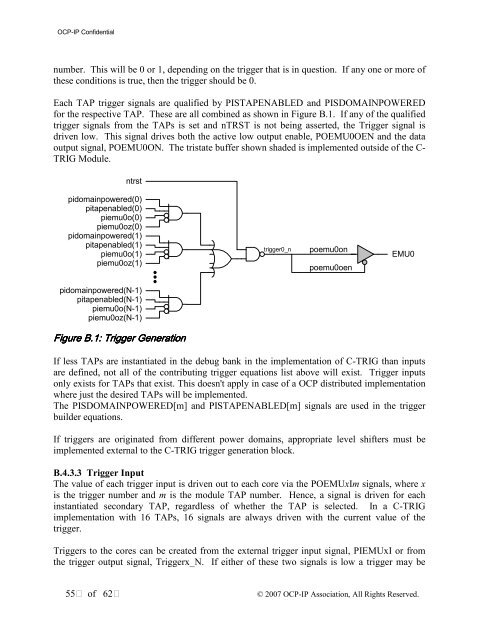

Each TAP trigger signals are qualified by PISTAPENABLED and PISDOMAINPOWERED<br />

for the respective TAP. These are all combined as shown in Figure B.1. If any of the qualified<br />

trigger signals from the TAPs is set and nTRST is not being asserted, the Trigger signal is<br />

driven low. This signal drives both the active low output enable, POEMU0OEN and the data<br />

output signal, POEMU0ON. The tristate buffer shown shaded is implemented outside of the C-<br />

TRIG Module.<br />

ntrst<br />

pidomainpowered(0)<br />

pitapenabled(0)<br />

piemu0o(0)<br />

piemu0oz(0)<br />

pidomainpowered(1)<br />

pitapenabled(1)<br />

piemu0o(1)<br />

piemu0oz(1)<br />

trigger0_n<br />

poemu0on<br />

poemu0oen<br />

EMU0<br />

pidomainpowered(N-1)<br />

pitapenabled(N-1)<br />

piemu0o(N-1)<br />

piemu0oz(N-1)<br />

Figure B.1: Trigger Generation<br />

If less TAPs are instantiated in the debug bank in the implementation of C-TRIG than inputs<br />

are defined, not all of the contributing trigger equations list above will exist. Trigger inputs<br />

only exists for TAPs that exist. This doesn't apply in case of a <strong>OCP</strong> distributed implementation<br />

where just the desired TAPs will be implemented.<br />

The PISDOMAINPOWERED[m] and PISTAPENABLED[m] signals are used in the trigger<br />

builder equations.<br />

If triggers are originated from different power domains, appropriate level shifters must be<br />

implemented external to the C-TRIG trigger generation block.<br />

B.4.3.3 Trigger Input<br />

The value of each trigger input is driven out to each core via the POEMUxIm signals, where x<br />

is the trigger number and m is the module TAP number. Hence, a signal is driven for each<br />

instantiated secondary TAP, regardless of whether the TAP is selected. In a C-TRIG<br />

implementation with 16 TAPs, 16 signals are always driven with the current value of the<br />

trigger.<br />

Triggers to the cores can be created from the external trigger input signal, PIEMUxI or from<br />

the trigger output signal, Triggerx_N. If either of these two signals is low a trigger may be<br />

55 of 62<br />

© 2007 <strong>OCP</strong>-<strong>IP</strong> Association, All Rights Reserved.