NAT-MCH Users Manual Version 1.16

NAT-MCH Users Manual Version 1.16

NAT-MCH Users Manual Version 1.16

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>NAT</strong>-<strong>MCH</strong> – <strong>Users</strong> <strong>Manual</strong><br />

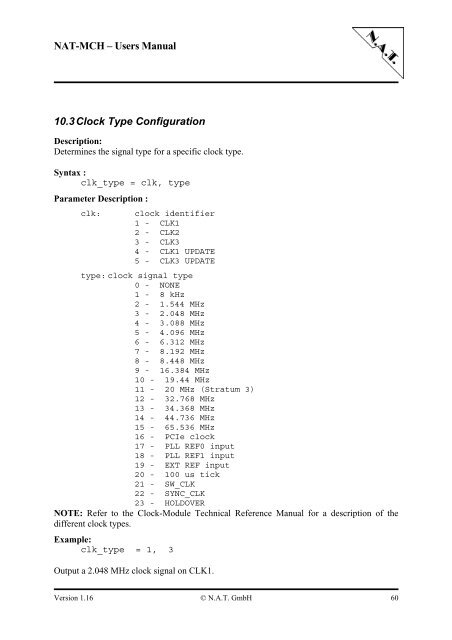

10.3 Clock Type Configuration<br />

Description:<br />

Determines the signal type for a specific clock type.<br />

Syntax :<br />

clk_type = clk, type<br />

Parameter Description :<br />

clk: clock identifier<br />

1 - CLK1<br />

2 - CLK2<br />

3 - CLK3<br />

4 - CLK1 UPDATE<br />

5 - CLK3 UPDATE<br />

type: clock signal type<br />

0 - NONE<br />

1 - 8 kHz<br />

2 - 1.544 MHz<br />

3 - 2.048 MHz<br />

4 - 3.088 MHz<br />

5 - 4.096 MHz<br />

6 - 6.312 MHz<br />

7 - 8.192 MHz<br />

8 - 8.448 MHz<br />

9 - 16.384 MHz<br />

10 - 19.44 MHz<br />

11 - 20 MHz (Stratum 3)<br />

12 - 32.768 MHz<br />

13 - 34.368 MHz<br />

14 - 44.736 MHz<br />

15 - 65.536 MHz<br />

16 - PCIe clock<br />

17 - PLL REF0 input<br />

18 - PLL REF1 input<br />

19 - EXT REF input<br />

20 - 100 us tick<br />

21 - SW_CLK<br />

22 - SYNC_CLK<br />

23 - HOLDOVER<br />

NOTE: Refer to the Clock-Module Technical Reference <strong>Manual</strong> for a description of the<br />

different clock types.<br />

Example:<br />

clk_type = 1, 3<br />

Output a 2.048 MHz clock signal on CLK1.<br />

<strong>Version</strong> <strong>1.16</strong> © N.A.T. GmbH 60