CHAPTER 3 METHODOLOGY 3.1 Overview The Water Monitoring ...

CHAPTER 3 METHODOLOGY 3.1 Overview The Water Monitoring ...

CHAPTER 3 METHODOLOGY 3.1 Overview The Water Monitoring ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

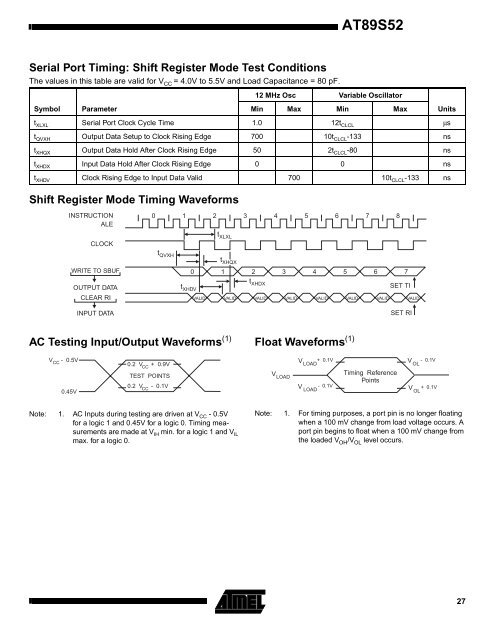

AT89S52Serial Port Timing: Shift Register Mode Test Conditions<strong>The</strong> values in this table are valid for V CC = 4.0V to 5.5V and Load Capacitance = 80 pF.12 MHz Osc Variable OscillatorSymbol ParameterMin Max Min Max Unitst XLXL Serial Port Clock Cycle Time 1.0 12t CLCL µst QVXH Output Data Setup to Clock Rising Edge 700 10t CLCL -133 nst XHQX Output Data Hold After Clock Rising Edge 50 2t CLCL -80 nst XHDX Input Data Hold After Clock Rising Edge 0 0 nst XHDV Clock Rising Edge to Input Data Valid 700 10t CLCL -133 nsShift Register Mode Timing WaveformsINSTRUCTIONALE012345678CLOCKt XHQXWRITE TO SBUF01234567OUTPUT DATAt QVXHt XLXLt XHDXt XHDVSET TICLEAR RIVALIDVALIDVALIDVALIDVALIDVALIDVALIDVALIDINPUT DATASET RIAC Testing Input/Output Waveforms (1)Float Waveforms (1)V - 0.5VCC 0.2 V + 0.9VCC0.45VTEST POINTS0.2 V - 0.1VCCVLOADV + 0.1VLOADV - 0.1V OLTiming ReferencePointsV LOAD - 0.1VV + 0.1V OLNote: 1. AC Inputs during testing are driven at V CC - 0.5Vfor a logic 1 and 0.45V for a logic 0. Timing measurementsare made at V IH min. for a logic 1 and V ILmax. for a logic 0.Note: 1. For timing purposes, a port pin is no longer floatingwhen a 100 mV change from load voltage occurs. Aport pin begins to float when a 100 mV change fromthe loaded V OH /V OL level occurs.27