VS1033 - MP3/AAC/WMA/MIDI AUDIO CODEC - VLSI Solution

VS1033 - MP3/AAC/WMA/MIDI AUDIO CODEC - VLSI Solution

VS1033 - MP3/AAC/WMA/MIDI AUDIO CODEC - VLSI Solution

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

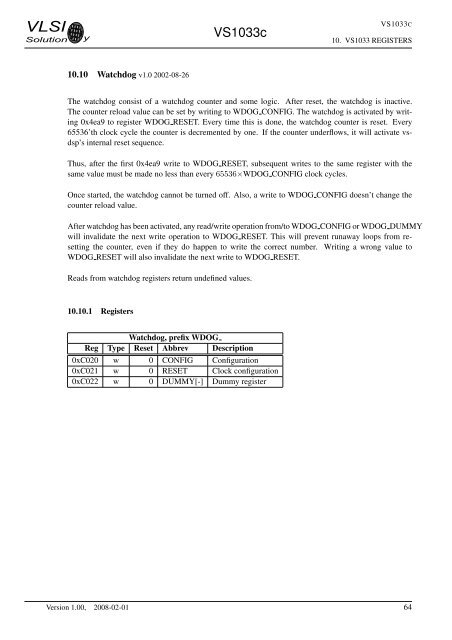

<strong>VLSI</strong><strong>Solution</strong> y<strong>VS1033</strong>c<strong>VS1033</strong>C10. <strong>VS1033</strong> REGISTERS10.10 Watchdog v1.0 2002-08-26The watchdog consist of a watchdog counter and some logic. After reset, the watchdog is inactive.The counter reload value can be set by writing to WDOG CONFIG. The watchdog is activated by writing0x4ea9 to register WDOG RESET. Every time this is done, the watchdog counter is reset. Every65536’th clock cycle the counter is decremented by one. If the counter underflows, it will activate vsdsp’sinternal reset sequence.Thus, after the first 0x4ea9 write to WDOG RESET, subsequent writes to the same register with thesame value must be made no less than every 65536×WDOG CONFIG clock cycles.Once started, the watchdog cannot be turned off. Also, a write to WDOG CONFIG doesn’t change thecounter reload value.After watchdog has been activated, any read/write operation from/to WDOG CONFIG or WDOG DUMMYwill invalidate the next write operation to WDOG RESET. This will prevent runaway loops from resettingthe counter, even if they do happen to write the correct number. Writing a wrong value toWDOG RESET will also invalidate the next write to WDOG RESET.Reads from watchdog registers return undefined values.10.10.1 RegistersWatchdog, prefix WDOGReg Type Reset Abbrev Description0xC020 w 0 CONFIG Configuration0xC021 w 0 RESET Clock configuration0xC022 w 0 DUMMY[-] Dummy registerVersion 1.00, 2008-02-01 64