SD Specifications Part 1 UHS-II Simplified Addendum - SD Association

SD Specifications Part 1 UHS-II Simplified Addendum - SD Association

SD Specifications Part 1 UHS-II Simplified Addendum - SD Association

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

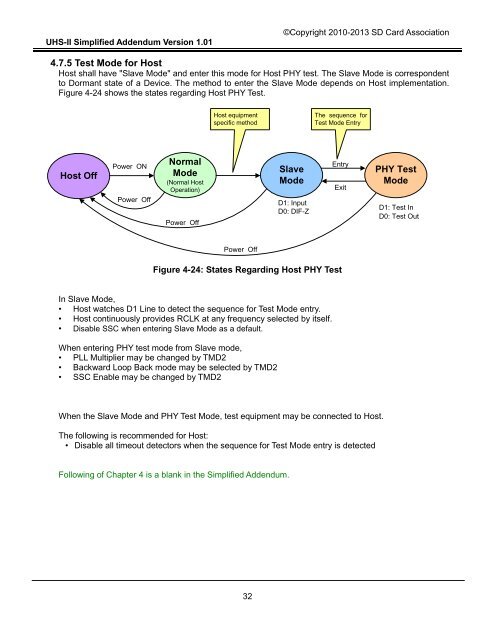

<strong>UHS</strong>-<strong>II</strong> <strong>Simplified</strong> <strong>Addendum</strong> Version 1.01©Copyright 2010-2013 <strong>SD</strong> Card <strong>Association</strong>4.7.5 Test Mode for HostHost shall have "Slave Mode" and enter this mode for Host PHY test. The Slave Mode is correspondentto Dormant state of a Device. The method to enter the Slave Mode depends on Host implementation.Figure 4-24 shows the states regarding Host PHY Test.Host equipmentspecific methodThe sequence forTest Mode EntryHost OffPower ONPower OffNormalMode(Normal HostOperation)Power OffSlaveModeD1: InputD0: DIF-ZEntryExitPHY TestModeD1: Test InD0: Test OutPower OffFigure 4-24: States Regarding Host PHY TestIn Slave Mode,• Host watches D1 Line to detect the sequence for Test Mode entry.• Host continuously provides RCLK at any frequency selected by itself.• Disable SSC when entering Slave Mode as a default.When entering PHY test mode from Slave mode,• PLL Multiplier may be changed by TMD2• Backward Loop Back mode may be selected by TMD2• SSC Enable may be changed by TMD2When the Slave Mode and PHY Test Mode, test equipment may be connected to Host.The following is recommended for Host:• Disable all timeout detectors when the sequence for Test Mode entry is detectedFollowing of Chapter 4 is a blank in the <strong>Simplified</strong> <strong>Addendum</strong>.32