Xilinx UG230 Spartan-3E FPGA Starter Kit Board User Guide

Xilinx UG230 Spartan-3E FPGA Starter Kit Board User Guide

Xilinx UG230 Spartan-3E FPGA Starter Kit Board User Guide

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 13: DDR SDRAM<br />

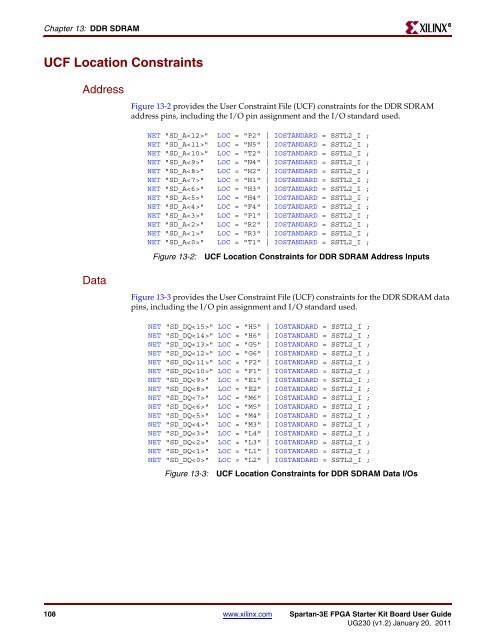

UCF Location Constraints<br />

Address<br />

Data<br />

Figure 13-2 provides the <strong>User</strong> Constraint File (UCF) constraints for the DDR SDRAM<br />

address pins, including the I/O pin assignment and the I/O standard used.<br />

NET "SD_A" LOC = "P2" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "N5" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "T2" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "N4" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "H2" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "H1" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "H3" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "H4" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "F4" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "P1" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "R2" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "R3" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_A" LOC = "T1" | IOSTANDARD = SSTL2_I ;<br />

Figure 13-2: UCF Location Constraints for DDR SDRAM Address Inputs<br />

Figure 13-3 provides the <strong>User</strong> Constraint File (UCF) constraints for the DDR SDRAM data<br />

pins, including the I/O pin assignment and I/O standard used.<br />

NET "SD_DQ" LOC = "H5" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "H6" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "G5" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "G6" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "F2" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "F1" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "E1" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "E2" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "M6" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "M5" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "M4" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "M3" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "L4" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "L3" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "L1" | IOSTANDARD = SSTL2_I ;<br />

NET "SD_DQ" LOC = "L2" | IOSTANDARD = SSTL2_I ;<br />

Figure 13-3: UCF Location Constraints for DDR SDRAM Data I/Os<br />

108 www.xilinx.com <strong>Spartan</strong>-<strong>3E</strong> <strong>FPGA</strong> <strong>Starter</strong> <strong>Kit</strong> <strong>Board</strong> <strong>User</strong> <strong>Guide</strong><br />

<strong>UG230</strong> (v1.2) January 20, 2011<br />

R