Xilinx UG230 Spartan-3E FPGA Starter Kit Board User Guide

Xilinx UG230 Spartan-3E FPGA Starter Kit Board User Guide

Xilinx UG230 Spartan-3E FPGA Starter Kit Board User Guide

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

R<br />

Chapter 14<br />

10/100 Ethernet Physical Layer Interface<br />

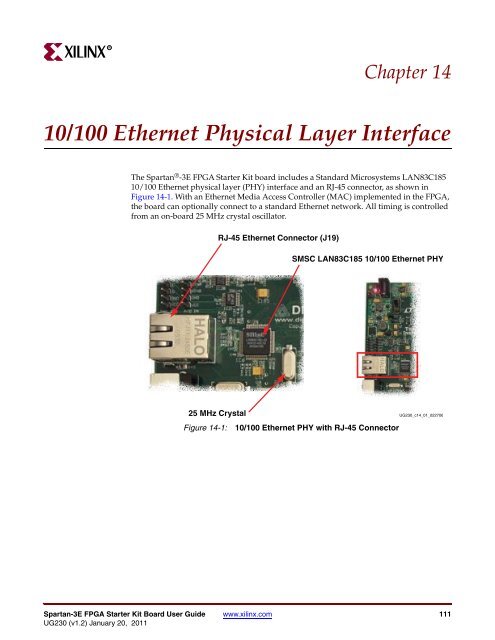

The <strong>Spartan</strong> ® -<strong>3E</strong> <strong>FPGA</strong> <strong>Starter</strong> <strong>Kit</strong> board includes a Standard Microsystems LAN83C185<br />

10/100 Ethernet physical layer (PHY) interface and an RJ-45 connector, as shown in<br />

Figure 14-1. With an Ethernet Media Access Controller (MAC) implemented in the <strong>FPGA</strong>,<br />

the board can optionally connect to a standard Ethernet network. All timing is controlled<br />

from an on-board 25 MHz crystal oscillator.<br />

RJ-45 Ethernet Connector (J19)<br />

SMSC LAN83C185 10/100 Ethernet PHY<br />

25 MHz Crystal <strong>UG230</strong>_c14_01_022706<br />

Figure 14-1: 10/100 Ethernet PHY with RJ-45 Connector<br />

<strong>Spartan</strong>-<strong>3E</strong> <strong>FPGA</strong> <strong>Starter</strong> <strong>Kit</strong> <strong>Board</strong> <strong>User</strong> <strong>Guide</strong> www.xilinx.com 111<br />

<strong>UG230</strong> (v1.2) January 20, 2011