User Manual

User Manual

User Manual

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

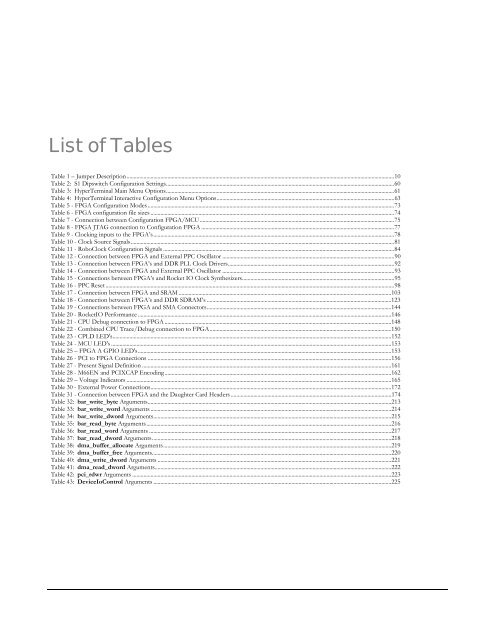

List of Tables<br />

Table 1 – Jumper Description..............................................................................................................................................................................................10<br />

Table 2: S1 Dipswitch Configuration Settings..................................................................................................................................................................60<br />

Table 3: HyperTerminal Main Menu Options..................................................................................................................................................................61<br />

Table 4: HyperTerminal Interactive Configuration Menu Options..............................................................................................................................63<br />

Table 5 - FPGA Configuration Modes ...............................................................................................................................................................................73<br />

Table 6 - FPGA configuration file sizes .............................................................................................................................................................................74<br />

Table 7 - Connection between Configuration FPGA/MCU..........................................................................................................................................75<br />

Table 8 - FPGA JTAG connection to Configuration FPGA .........................................................................................................................................77<br />

Table 9 - Clocking inputs to the FPGA’s...........................................................................................................................................................................78<br />

Table 10 - Clock Source Signals...........................................................................................................................................................................................81<br />

Table 11 - RoboClock Configuration Signals ....................................................................................................................................................................84<br />

Table 12 - Connection between FPGA and External PPC Oscillator ..........................................................................................................................90<br />

Table 13 - Connection between FPGA’s and DDR PLL Clock Drivers......................................................................................................................92<br />

Table 14 - Connection between FPGA and External PPC Oscillator ..........................................................................................................................93<br />

Table 15 - Connections between FPGA’s and Rocket IO Clock Synthesizers............................................................................................................95<br />

Table 16 - PPC Reset .............................................................................................................................................................................................................98<br />

Table 17 - Connection between FPGA and SRAM .......................................................................................................................................................103<br />

Table 18 - Connection between FPGA’s and DDR SDRAM’s ...................................................................................................................................123<br />

Table 19 - Connections between FPGA and SMA Connectors...................................................................................................................................144<br />

Table 20 - RocketIO Performance ....................................................................................................................................................................................146<br />

Table 21 - CPU Debug connection to FPGA .................................................................................................................................................................148<br />

Table 22 - Combined CPU Trace/Debug connection to FPGA.................................................................................................................................150<br />

Table 23 - CPLD LED's......................................................................................................................................................................................................152<br />

Table 24 - MCU LED's .......................................................................................................................................................................................................153<br />

Table 25 – FPGA A GPIO LED's....................................................................................................................................................................................153<br />

Table 26 - PCI to FPGA Connections .............................................................................................................................................................................156<br />

Table 27 - Present Signal Definition .................................................................................................................................................................................161<br />

Table 28 - M66EN and PCIXCAP Encoding.................................................................................................................................................................162<br />

Table 29 – Voltage Indicators ............................................................................................................................................................................................165<br />

Table 30 - External Power Connections...........................................................................................................................................................................172<br />

Table 31 - Connection between FPGA and the Daughter Card Headers ..................................................................................................................174<br />

Table 32: bar_write_byte Arguments.............................................................................................................................................................................213<br />

Table 33: bar_write_word Arguments ...........................................................................................................................................................................214<br />

Table 34: bar_write_dword Arguments.........................................................................................................................................................................215<br />

Table 35: bar_read_byte Arguments..............................................................................................................................................................................216<br />

Table 36: bar_read_word Arguments ............................................................................................................................................................................217<br />

Table 37: bar_read_dword Arguments..........................................................................................................................................................................218<br />

Table 38: dma_buffer_allocate Arguments..................................................................................................................................................................219<br />

Table 39: dma_buffer_free Arguments..........................................................................................................................................................................220<br />

Table 40: dma_write_dword Arguments ......................................................................................................................................................................221<br />

Table 41: dma_read_dword Arguments........................................................................................................................................................................222<br />

Table 42: pci_rdwr Arguments ........................................................................................................................................................................................223<br />

Table 43: DeviceIoControl Arguments .........................................................................................................................................................................225

![SODIMM Schematic [PDF]](https://img.yumpu.com/43758171/1/190x146/sodimm-schematic-pdf.jpg?quality=85)

![User's Manual [PDF - 8.3MB]](https://img.yumpu.com/36435641/1/190x245/users-manual-pdf-83mb.jpg?quality=85)