- Page 1 and 2: THE DINI GROUP LOGIC Emulation Sour

- Page 3 and 4: Table of Contents ABOUT THIS MANUAL

- Page 5 and 6: 4.6 Power PC (PPC) Clock - Sytem Cl

- Page 7 and 8: 2.11.1 Description ................

- Page 9 and 10: Figure 54 - Assembly drawing for th

- Page 11 and 12: ABOUT THIS MANUAL Chapter 1 About T

- Page 13 and 14: ABOUT THIS MANUAL Convention Meanin

- Page 15 and 16: ABOUT THIS MANUAL Samir Palnitkar,

- Page 17 and 18: GETTING STARTED Virtex-II Pro FPGA

- Page 19 and 20: GETTING STARTED Figure 2 - Default

- Page 21 and 22: GETTING STARTED Jumper Installed Si

- Page 23 and 24: GETTING STARTED 3.5 PPC RS232 Port

- Page 25 and 26: GETTING STARTED by The Dini Group.

- Page 27 and 28: GETTING STARTED 7. The AETEST Test

- Page 29 and 30: INTRODUCTION TO VIRTEX-II PRO AAND

- Page 31 and 32: INTRODUCTION TO VIRTEX-II PRO AAND

- Page 33 and 34: INTRODUCTION TO VIRTEX-II PRO AAND

- Page 35 and 36: INTRODUCTION TO VIRTEX-II PRO AAND

- Page 37 and 38: INTRODUCTION TO VIRTEX-II PRO AAND

- Page 39: INTRODUCTION TO VIRTEX-II PRO AAND

- Page 43 and 44: INTRODUCTION TO VIRTEX-II PRO AAND

- Page 45 and 46: INTRODUCTION TO THE SOFTWARE TOOLS

- Page 47 and 48: INTRODUCTION TO THE SOFTWARE TOOLS

- Page 49 and 50: INTRODUCTION TO THE SOFTWARE TOOLS

- Page 51 and 52: INTRODUCTION TO THE SOFTWARE TOOLS

- Page 53 and 54: INTRODUCTION TO THE SOFTWARE TOOLS

- Page 55 and 56: INTRODUCTION TO THE SOFTWARE TOOLS

- Page 57 and 58: PROGRAMMING/CONFIGURING THE HARDWAR

- Page 59 and 60: PROGRAMMING/CONFIGURING THE HARDWAR

- Page 61 and 62: PROGRAMMING/CONFIGURING THE HARDWAR

- Page 63 and 64: PROGRAMMING/CONFIGURING THE HARDWAR

- Page 65 and 66: PROGRAMMING/CONFIGURING THE HARDWAR

- Page 67 and 68: PROGRAMMING/CONFIGURING THE HARDWAR

- Page 69 and 70: PROGRAMMING/CONFIGURING THE HARDWAR

- Page 71 and 72: PROGRAMMING/CONFIGURING THE HARDWAR

- Page 73 and 74: PROGRAMMING/CONFIGURING THE HARDWAR

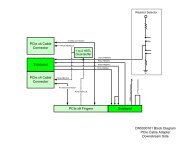

- Page 75 and 76: 1 BOARD HARDWARE Chapter 7 Board Ha

- Page 77 and 78: BOARD HARDWARE • ~5900 Kbits of B

- Page 79 and 80: BOARD HARDWARE MCU_A0 MCU_A1 MCU_A2

- Page 81 and 82: BOARD HARDWARE • Receive Data TXD

- Page 83 and 84: BOARD HARDWARE +3.3V +3.3V J6 1 2 3

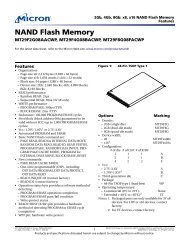

- Page 85 and 86: BOARD HARDWARE SM_CLE SM_ALE SM_WEn

- Page 87 and 88: BOARD HARDWARE Table 8 - FPGA JTAG

- Page 89 and 90: BOARD HARDWARE USER_BCLKp U16.AP21

- Page 91 and 92:

BOARD HARDWARE DDR_FCLKp U54.AT21 U

- Page 93 and 94:

BOARD HARDWARE Eighteen configurabl

- Page 95 and 96:

BOARD HARDWARE Signal Name Descript

- Page 97 and 98:

BOARD HARDWARE Signal Name Descript

- Page 99 and 100:

BOARD HARDWARE 4.3.5 Customizing th

- Page 101 and 102:

BOARD HARDWARE positive clock and t

- Page 103 and 104:

BOARD HARDWARE DDR_DCLKn U35.AU21 U

- Page 105 and 106:

BOARD HARDWARE Figure 29 - REFCLK/B

- Page 107 and 108:

BOARD HARDWARE +1.5V +2.5V +3.3V +5

- Page 109 and 110:

BOARD HARDWARE SRAM1_A0 SRAM1_A1 SR

- Page 111 and 112:

BOARD HARDWARE Figure 33 - SSRAM Pi

- Page 113 and 114:

BOARD HARDWARE 6.1.2 SSRAM Clocking

- Page 115 and 116:

BOARD HARDWARE Signal Name SRAM Pin

- Page 117 and 118:

BOARD HARDWARE Signal Name SRAM Pin

- Page 119 and 120:

BOARD HARDWARE Signal Name SRAM Pin

- Page 121 and 122:

BOARD HARDWARE Signal Name SRAM Pin

- Page 123 and 124:

BOARD HARDWARE Signal Name SRAM Pin

- Page 125 and 126:

BOARD HARDWARE Signal Name SRAM Pin

- Page 127 and 128:

BOARD HARDWARE Signal Name SRAM Pin

- Page 129 and 130:

BOARD HARDWARE 6.2 DDR SDRAM Double

- Page 131 and 132:

BOARD HARDWARE SSTL2 Class 1 termin

- Page 133 and 134:

BOARD HARDWARE Table 18 - Connectio

- Page 135 and 136:

BOARD HARDWARE Signal Name FPGA Pin

- Page 137 and 138:

BOARD HARDWARE Signal Name FPGA Pin

- Page 139 and 140:

BOARD HARDWARE Signal Name FPGA Pin

- Page 141 and 142:

BOARD HARDWARE Signal Name FPGA Pin

- Page 143 and 144:

BOARD HARDWARE Signal Name FPGA Pin

- Page 145 and 146:

BOARD HARDWARE Signal Name FPGA Pin

- Page 147 and 148:

BOARD HARDWARE Signal Name FPGA Pin

- Page 149 and 150:

BOARD HARDWARE Signal Name FPGA Pin

- Page 151 and 152:

BOARD HARDWARE Signal Name FPGA Pin

- Page 153 and 154:

BOARD HARDWARE Signal Name FPGA Pin

- Page 155 and 156:

BOARD HARDWARE Signal Name FPGA Pin

- Page 157 and 158:

BOARD HARDWARE The PowerPC 405 CPU

- Page 159 and 160:

BOARD HARDWARE Signal Name FPGA Pin

- Page 161 and 162:

BOARD HARDWARE Signal Name FPGA Pin

- Page 163 and 164:

BOARD HARDWARE Signal Name Device L

- Page 165 and 166:

BOARD HARDWARE power to the DN6000k

- Page 167 and 168:

BOARD HARDWARE Signal Name Connecto

- Page 169 and 170:

BOARD HARDWARE Signal Name Connecto

- Page 171 and 172:

BOARD HARDWARE Signal Name Connecto

- Page 173 and 174:

BOARD HARDWARE 10.2.3 Further Infor

- Page 175 and 176:

BOARD HARDWARE J2 +3.3V TP1 +12V +1

- Page 177 and 178:

BOARD HARDWARE DN6000K10PCI User Gu

- Page 179 and 180:

BOARD HARDWARE 12.2 DN3000K10SD Dau

- Page 181 and 182:

BOARD HARDWARE and the IDT74LVC1624

- Page 183 and 184:

BOARD HARDWARE 12.2.3 Unbuffered IO

- Page 185 and 186:

BOARD HARDWARE Daughter Card Connec

- Page 187 and 188:

BOARD HARDWARE Daughter Card Connec

- Page 189 and 190:

BOARD HARDWARE Daughter Card Connec

- Page 191 and 192:

BOARD HARDWARE Daughter Card Connec

- Page 193 and 194:

BOARD HARDWARE Daughter Card Connec

- Page 195 and 196:

BOARD HARDWARE Daughter Card Connec

- Page 197 and 198:

BOARD HARDWARE Daughter Card Connec

- Page 199 and 200:

BOARD HARDWARE Daughter Card Connec

- Page 201 and 202:

BOARD HARDWARE Daughter Card Connec

- Page 203 and 204:

BOARD HARDWARE Daughter Card Connec

- Page 205 and 206:

BOARD HARDWARE Daughter Card Connec

- Page 207 and 208:

BOARD HARDWARE Daughter Card Connec

- Page 209 and 210:

BOARD HARDWARE The DN6000K10PCI PWB

- Page 211 and 212:

FPGA A Start End Address Read / Des

- Page 213 and 214:

FPGA B Start Address End Address Re

- Page 215 and 216:

FPGA D Start End Address Read / Des

- Page 217 and 218:

FPGA F Start End Address Read / Des

- Page 219 and 220:

Appendix B - AETEST 1 AETEST Instal

- Page 221 and 222:

Follow the procedures listed below

- Page 223 and 224:

2 AETEST Basic C++ Functions The AE

- Page 225 and 226:

2.3 bar_write_dword bar_write_dword

- Page 227 and 228:

2.5 bar_read_word bar_read_word is

- Page 229 and 230:

2.7 dma_buffer_allocate dma_buffer_

- Page 231 and 232:

2.9 dma_write_dword dma_write_dword

- Page 233 and 234:

2.11 pci_rdwr pci_rdwr is a functio

- Page 235 and 236:

2.12 DeviceIoControl DeviceIoContro

- Page 237:

2.12.5 Derived Functions The follow

![SODIMM Schematic [PDF]](https://img.yumpu.com/43758171/1/190x146/sodimm-schematic-pdf.jpg?quality=85)

![User's Manual [PDF - 8.3MB]](https://img.yumpu.com/36435641/1/190x245/users-manual-pdf-83mb.jpg?quality=85)