User Manual

User Manual

User Manual

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

INTRODUCTION TO THE SOFTWARE TOOLS<br />

make INCLUDE_DDR2<br />

make EXCLUDE_DDR2<br />

make DDR_32_MEG<br />

make DDR_64_MEG<br />

make DDR_128_MEG<br />

makes changes to synplicity projects, EDK source code,<br />

and UCF files to include DDR2<br />

makes changes to synplicity projects, EDK source code,<br />

and UCF files to exclude DDR2<br />

makes changes to synplicity projects and EDK source<br />

code to set DDR size<br />

makes changes to synplicity projects and EDK source<br />

code to set DDR size<br />

makes changes to synplicity projects and EDK source<br />

code to set DDR size<br />

The reference design must support any number of FPGA's in both VP70 and VP100<br />

sizes. Compiler constants are used to include/exclude code, as well as to set<br />

appropriate parameters for the configuration being compiled for. Specifically, the user<br />

may want to include/exclude any memory device (DDR1, DDR2, SRAM), or may<br />

want to switch between the VP70 and VP100 part. There are four places where<br />

changes must be made to get the desired configuration:<br />

I. Synplicity synthesis project file<br />

II. UCF files in 'source/ucf'<br />

III. Xilinx EDK project file<br />

IV. Xilinx EDK processor so urce code files ('PPC/code/fpga_params/*.h')<br />

V. Setting up the build utility: "make.bat"<br />

Note that the build utility runs the xilinx tools from the command line, so there are no<br />

Xilinx Project Navigator files to edit. If you choose to use the Project Navigator GUI,<br />

be very careful to have all the appropriate settings (ie 2vp70 vs 2vp100) The following<br />

sections explain what to change and what options the user has to accomplish these<br />

changes (Most are automated, some are not). It is highly recommended that everything<br />

be recompiled after making any of these changes, including the PPC netlist, the<br />

synplicity project, the Xilinx project, and the EDK source code. If everything is not<br />

updated properly unpredictable behavior will result. If you aren't sure, delete all tool<br />

generated files and start fresh. For information on the usage of the build tool<br />

(make.bat), see the top of the ' make.bat' file.<br />

I. SYNPLICITY SYNTHESIS PROJECT FILE<br />

In the 'synthesis' folder there are six project files, one for each FPGA. The line<br />

'set_option -part XC2VP70' must be modified appropriately for the VP70 or VP100.<br />

This change, as well as changes to the parameters described below may be made<br />

DN6000K10PCI <strong>User</strong> Guide www.dinigroup.com 40

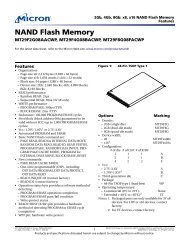

![SODIMM Schematic [PDF]](https://img.yumpu.com/43758171/1/190x146/sodimm-schematic-pdf.jpg?quality=85)

![User's Manual [PDF - 8.3MB]](https://img.yumpu.com/36435641/1/190x245/users-manual-pdf-83mb.jpg?quality=85)