mitsubishi - Al Kossow's Bitsavers

mitsubishi - Al Kossow's Bitsavers

mitsubishi - Al Kossow's Bitsavers

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

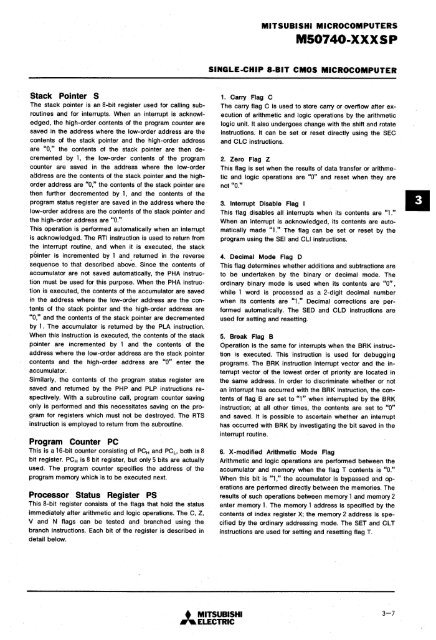

MITSUBISHI MICROCOMPUTERSMS0740-XXXS PSINGLE-CHIP 8-BIT CMOS MICROCOMPUTERStack Pointer SThe stack pointer is an 8-bit register used for calling subroutinesand for interrupts. When an interrupt is acknowledged,the high-order contents of the program counter aresaved in the address where the low-order address are thecontents of the stack pointer and the high-order addressare "0," the contents of the stack pointer are then decrementedby 1, the low-order contents of the programcounter are saved in the address where the low-orderaadress are the contents of the stack pointer .and the highorderaddress are "0," the contents of the stack pointer arethen further decremented by 1, and the contents of theprogram status register are saved in the address where thelow-order address are the contents of the stack pointer andthe high-order address are "0."This operation is performed automatically when an interruptis acknowledged. The RTI instruction is used to return fromthe interrupt routine, and when it is executed, the stackp6inter is incremented by 1 and returned in the reversesequence to that described abo~e. Since the contents ofaccumulator are not saved automatically, the PHA instructionmust be used for this purpose. When the PHA instructionis executed, the contents of the accumulator are savedin the address where the low-order address are the contentsof the stack pointer and the high-order address are"0," and the contents of the stack pointer are decrementedby 1. The accumulator is returned by the PLA instruction.When this instruction is executed, the contents of the stackpointer are incremented by 1 and the contents of theaddress where the low-order address are the stack pointercontents and the high-order address are "0" enter theaccumulator.Similarly, the contents of the program status register aresaved and returned by the PHP and PLP instructions respectively.With a subroutine call, program counter savingonly is performed and this necessitates saving on the programfor registers which must not be destroyed. The RTSinstruction is employed to return from the subroutine.Program Counter PCThis is a 16-bit counter consisting of PC H and PCL, both is 8bit register. PC H is 8 bit register, but only 5 bits are actuallyused. The program counter specifies the address of theprogram memory whicA is to be executed next.Processor. Status Register PSThis 8-bit register consists of the flags that hold the statusimmediately after arithmetic and logic operations. The C, Z,V and· N flags can be tested and. branched using thebranch instructions. Each bit of the register is described indetail below.1. Carry Flag CThe carry flag C is used to store carry or overflow after executionof arithmetic and logic operations by the arithmeticlogic unit. It also undergoes change with the shift and rotateinstructions. It can be set or reset directly using the SECand CLC instructions.2. Zero Flag ZThis flag is set when the results of data transfer or arithmeticand logic operations are "0" and reset when they arenot "0."3. Interrupt Disable Flag IThis flag disables all interrupts when its contents are "1."When an interrupt is acknowledged, its contents are automaticallymade "1." The flag can be set or reset by theprogram using the SEI and CLI instructions.4. Decimal Mode Flag DThis flag determines whether additions and subtractions areto be undertaken by the binary or decimal mode. Theordinary binary mode is used when its contents are "0",while 1 word is processed as a 2-digit decimal numberwhen its contents are "1." Decimal corrections are performedautomatically. The SED and CLD instructions areused for setting and resetting.5. Break Flag BOperation is the same for interrupts when the BRK instructionis executed. This Instruction is used for debuggingprograms. The BRK instruction interrupt vector and the interruptvector of the lowest order of priority are located inthe same address. In order to discriminate whether or notan interrupt has occurred with the BRK instruction, the contentsof flag B are set to "1" when interrupted by the BRKinstruction; at all other times, the contents are set to "0"and saved. It is possible to ascertain whether an interrupthas occurred with BRK by investigating the bit saved in theinterrupt routine.6. X-modified Arithmetic Mode FlagArithmetic and logic operations are performed between theaccumulator and memory when the flag T contents is "0."When this bit is "1," the accumulator is bypassed and operationsare performed directly between the memories. Theresults of such operations between memory 1 and memory 2enter memory 1. The memory 1 address is specified by thecontents of index register X; the memory 2 address is specifiedby the ordinary addressing mode. The SET and CL Tinstructions are used for setting and resetting flag T.II• MITSUBISHI.... ELECTRIC3-7