You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

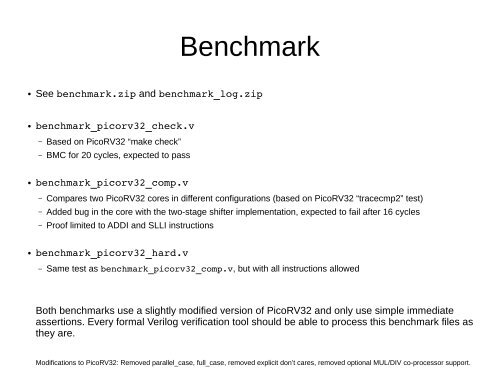

Benchmark<br />

●<br />

See benchmark.zip and benchmark_log.zip<br />

●<br />

benchmark_picorv32_check.v<br />

– Based on PicoRV32 “make check”<br />

– BMC for 20 cycles, expected to pass<br />

●<br />

benchmark_picorv32_comp.v<br />

– Compares two PicoRV32 cores in different configurations (based on PicoRV32 “tracecmp2” test)<br />

– Added bug in the core <strong>with</strong> the two-stage shifter implementation, expected to fail after 16 cycles<br />

– Proof limited to ADDI and SLLI instructions<br />

●<br />

benchmark_picorv32_hard.v<br />

– Same test as benchmark_picorv32_comp.v, but <strong>with</strong> all instructions allowed<br />

Both benchmarks use a slightly modified version of PicoRV32 and only use simple immediate<br />

assertions. Every formal Verilog verification tool should be able to process this benchmark files as<br />

they are.<br />

Modifications to PicoRV32: Removed parallel_case, full_case, removed explicit don’t cares, removed optional MUL/DIV co-processor support.