- Page 3 and 4:

PBRNYATAANDengan ini saya menyataka

- Page 5 and 6:

vPRAKATASungguh suatu anugerah yang

- Page 7 and 8:

viiDAFTAR ISIhalamanHALAMAN JUDUL..

- Page 9:

ix4.1.3. Pengujian zig-zag buffer..

- Page 12 and 13:

xiiDAFTAR TABELhalamanTabel 1.1 Beb

- Page 14 and 15:

xivINTISARIImplementasi kompresi ci

- Page 16 and 17:

1BAB IPENDAHULUAN1.1. Latar Belakan

- Page 19 and 20:

4Perancangan prototype rangkaian di

- Page 21 and 22:

6BAB IITINJAUAN PUSTAKA DAN DASAR T

- Page 23 and 24:

8dua matriks 4x4. Pengali yang dibu

- Page 25 and 26:

kompresi, data citra dalam memori d

- Page 27 and 28:

F=G =[1 0 0 0 0 0 0 0 00]0 1 0 0 0

- Page 29 and 30:

14Pada dasarnya C s pada persamaan

- Page 31 and 32:

16demikian, berdasarkan spesifikasi

- Page 33 and 34:

18Gambar 2.2 Urutan pengeluaran dat

- Page 35 and 36:

Tabel 2.3 Kode Huffman untuk pemeta

- Page 37 and 38:

Hasil dari proses tersebut adalah s

- Page 39 and 40:

24rangkaian yang kompleks, VHDL cuk

- Page 41 and 42:

263.3.1. Perancangan sistem secara

- Page 43 and 44:

28data hasil kompresi dikeluarkan m

- Page 45 and 46:

30untuk memasukkan seluruh data. Be

- Page 47 and 48:

32diakuisisi, kemudian data output

- Page 49 and 50: 34case cnt iswhen "0000" => -- stat

- Page 51 and 52: 36ofset3(k downto 1)'0');ofset3(0)

- Page 53 and 54: 38m3 = cos(2*π/16) cos(6*π/16) =

- Page 55 and 56: 40dalam memori, data dari memori te

- Page 57 and 58: Definisi input dan output pada tran

- Page 59 and 60: 44.....end if;Pengaksesan alamat ba

- Page 61 and 62: 46Q k =Gambar 3.10 Struktur unit zi

- Page 63 and 64: 48ZigzagbufferOut14 bit 22 bit 9 bi

- Page 65 and 66: 50Gambar 3.13 Diagram blok sub modu

- Page 67 and 68: 52Gambar 3.15 Rangkaian penyandi RL

- Page 69 and 70: 543.3.17. Code MultiplexerDalam ran

- Page 71 and 72: 56sebagai data uji adalah data citr

- Page 73 and 74: 58Simulator VHDL pada penelitian in

- Page 75 and 76: 60untuk mengkonversi keluaran seria

- Page 77 and 78: n, sedangkan bn berarti baris ke-n.

- Page 79 and 80: 64b. Analisis diagram pewaktuanSimu

- Page 81 and 82: 66(d)(e)Gambar 4.2 (a - e). Diagram

- Page 83 and 84: 68Gambar 4.3 Simulasi awal pengisia

- Page 85 and 86: 70blok dapat berjalan bersamaan. Pa

- Page 87 and 88: Tabel 4.4 Hasil komputasi DCT-2D te

- Page 89 and 90: 74Gambar 4.8 Diagram pewaktuan inpu

- Page 91 and 92: 76Tingkat kesalahan pada bagian ini

- Page 93 and 94: 784.1.6 Pengujian unit penghasil ni

- Page 95 and 96: 80Gambar 4.13 Diagram pewaktuan uni

- Page 97 and 98: Kode pada Tabel 4.8 disusun dari ni

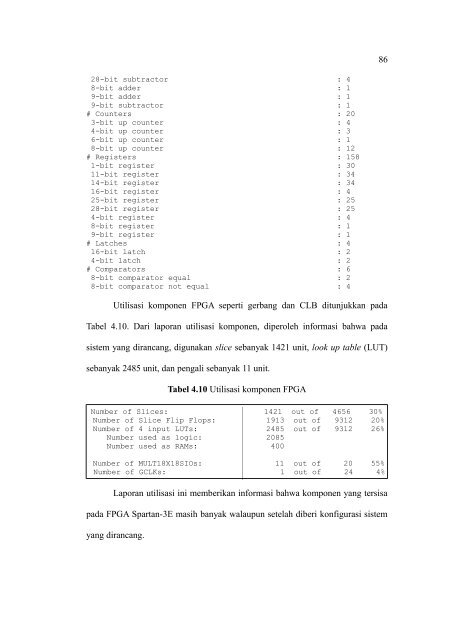

- Page 99: 84atau pemulihan citra tersebut dib

- Page 103 and 104: 88cascade dan tidak pipelined. Berd

- Page 105 and 106: 90240x320 adalah 2,7 ms sedangkan u

- Page 107 and 108: oleh FPGA cukup mendekati rasio kom

- Page 109 and 110: tetapi tidak ditemukan distorsi. Ji

- Page 111 and 112: 96Berdasarkan percobaan, pada pengi

- Page 113 and 114: 98BAB VKESIMPULAN DAN SARAN5.1. Kes

- Page 115 and 116: 100menampung data citra input dan d

- Page 117 and 118: 102International, New Jersey, 1989.

- Page 119 and 120: . Hasil Kompresirasio kompresi = 10

- Page 121 and 122: . Hasil Kompresirasio kompresi = 13

- Page 123 and 124: . Hasil kompresirasio kompresi = 9

- Page 125 and 126: . Hasil kompresirasio kompresi = 12

- Page 127 and 128: Source code root enkoder JPEG (jpeg

- Page 129 and 130: --addr_max'0');elsif(rising_edge(cl

- Page 131 and 132: -- clr_tmp

- Page 133 and 134: n:integer:=10;--MSB data inputk:int

- Page 135 and 136: st=>rst,en_dct=>en_dct2,vin=>dout(1

- Page 137 and 138: signal d8: std_logic_vector(k downt

- Page 139 and 140: ofset5'0');ofset6'0');ofset7'0');el

- Page 141 and 142: ofset3(0)

- Page 143 and 144: signal d0: std_logic_vector(k downt

- Page 145 and 146: s5'0');s6'0');s7'0');ofset0'0');ofs

- Page 147 and 148: --end if;when "0110" =>vin_6

- Page 149 and 150: om_in:in std_logic_vector(lebar_rom

- Page 151 and 152:

use ieee.std_logic_1164.all;use iee

- Page 153 and 154:

st: in std_logic;dc: in std_logic;d

- Page 155 and 156:

cat:out std_logic_vector(3 downto 0

- Page 157 and 158:

end if;end if;end process;end behav

- Page 159 and 160:

tmp

- Page 161 and 162:

tmp_rom(58)

- Page 163 and 164:

tmp_rom(244)

- Page 165 and 166:

tmp_rom(106)

- Page 167 and 168:

eginprocess(dc_cat) beginif(dc_cat=

- Page 169 and 170:

signal tmphuff,tmpsym: std_logic_ve

- Page 171 and 172:

entity controller isport(clk: in st

- Page 173 and 174:

dc

- Page 175 and 176:

un,cat huffman code6,4 111111111010