轻松实现高速串行I/O

轻松实现高速串行I/O

轻松实现高速串行I/O

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

SERDES 示例资料—RocketIO X 收发器概述<br />

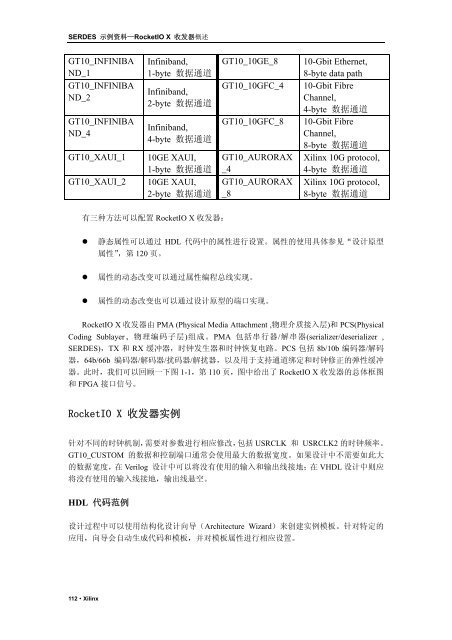

GT10_INFINIBA<br />

ND_1<br />

GT10_INFINIBA<br />

ND_2<br />

GT10_INFINIBA<br />

ND_4<br />

Infiniband,<br />

1-byte 数据通道<br />

Infiniband,<br />

2-byte 数据通道<br />

Infiniband,<br />

4-byte 数据通道<br />

GT10_XAUI_1 10GE XAUI,<br />

1-byte 数据通道<br />

GT10_XAUI_2 10GE XAUI,<br />

2-byte 数据通道<br />

有三种方法可以配置 RocketIO X 收发器:<br />

GT10_10GE_8 10-Gbit Ethernet,<br />

8-byte data path<br />

GT10_10GFC_4 10-Gbit Fibre<br />

Channel,<br />

4-byte 数据通道<br />

GT10_10GFC_8 10-Gbit Fibre<br />

Channel,<br />

8-byte 数据通道<br />

GT10_AURORAX Xilinx 10G protocol,<br />

_4<br />

4-byte 数据通道<br />

GT10_AURORAX Xilinx 10G protocol,<br />

_8<br />

8-byte 数据通道<br />

静态属性可以通过 HDL 代码中的属性进行设置。属性的使用具体参见“设计原型<br />

属性”,第 120 页。<br />

属性的动态改变可以通过属性编程总线实现。<br />

属性的动态改变也可以通过设计原型的端口实现。<br />

RocketIO X 收发器由 PMA (Physical Media Attachment ,物理介质接入层)和 PCS(Physical<br />

Coding Sublayer,物理编码子层)组成。PMA 包括串行器/解串器(serializer/deserializer ,<br />

SERDES),TX 和 RX 缓冲器,时钟发生器和时钟恢复电路。PCS 包括 8b/10b 编码器/解码<br />

器,64b/66b 编码器/解码器/扰码器/解扰器,以及用于支持通道绑定和时钟修正的弹性缓冲<br />

器。此时,我们可以回顾一下图 1-1,第 110 页,图中给出了 RocketIO X 收发器的总体框图<br />

和 FPGA 接口信号。<br />

RocketIO X 收发器实例<br />

针对不同的时钟机制,需要对参数进行相应修改,包括 USRCLK 和 USRCLK2 的时钟频率。<br />

GT10_CUSTOM 的数据和控制端口通常会使用最大的数据宽度。如果设计中不需要如此大<br />

的数据宽度,在 Verilog 设计中可以将没有使用的输入和输出线接地;在 VHDL 设计中则应<br />

将没有使用的输入线接地,输出线悬空。<br />

HDL 代码范例<br />

设计过程中可以使用结构化设计向导(Architecture Wizard)来创建实例模板。针对特定的<br />

应用,向导会自动生成代码和模板,并对模板属性进行相应设置。<br />

112·Xilinx