轻松实现高速串行 I/O· 某些情况需要使用4个符号的时钟修正序列。时钟修正通过检测接收FIFO来完成其工作。如 果FIFO接近于满,则查找下一个时钟修正序列而不将数据序列写入FIFO。这种操作称作丢 弃。相反地,如果FIFO接近于空,则查找下一个时钟修正序列,同时它会被两次写入FIFO。 这种操作通常也称作重复。 时钟修正进行的频数必须足够多,从而可以通过丢弃或者重复来补偿时钟的差异。时钟 修正序列和idle序列通常也是一样的。 有些系统并不需要时钟修正。例如,在很多芯片到芯片(chip-to-chip)的应用中,同一 个振荡器为所有收发器提供参考时钟。相同的参考时钟和相同的速率意味着不需要进行时钟 修正。同样,如果所有接收电路的时钟都来自恢复时钟,那么时钟修正也是不需要的。如果 FIFO的写入速率和读出速率相等,也没有必要进行时钟修正。 如果所有的传输参考时钟都是通过一个外部的PLL锁定在一个公共的参考频率上,那么 也不需要时钟修正。对于高精确度的串行数字视频链路来说,这是常用的一种结构。所有的 传输时钟都是从一个公共的视频参考中获取的。无法锁定到这个信号往往将导致自由滑动的 视频流,相对于其他的锁定信号。在1G或2G速率上实现是比较简单的,但是设计一个能够 用于10Gb链路且有足够精度的参考时钟是非常有挑战性的。 表 3-4给出了在不同晶振频率和晶振精度下时钟修正序列之间的最大时钟周期数。 表3-4 时钟修正表 振荡 器频 率 (MHz) 晶振 精度 (PPM) 线路 速率 (GB/s) Fmax (MHz) Fmin (MHz) 差异/ 周期 (ps) Remove1 序列 修正前的最大周期数 Remove2 序列 Remove3 序列 Remove 4 序列 156.25 100 3.125 156.2656 156.2344 1.2800 4,999 9,999 14,998 19,998 156.25 50 3.125 156.2578 156.2422 0.6400 9,999 19,998 29,998 ‘39,997 156.25 20 3.125 156.2531 156.2469 0.2560 24,999 49,999 74,998 99,998 125 100 2.500 125.0125 124.9875 1.6000 4,999 9,998 14,998 19,997 125 50 2.500 125.0063 124.9938 0.8000 9,999 19,998 29,998 ‘39,997 125 20 2.500 125.0025 124.9975 0.3200 24,999 49,998 74,998 99,997 62.5 100 1.250 62.5063 62.4938 3.2000 4,999 9,998 14,998 19,997 62.5 50 1.250 62.5031 62.4969 1.6000 9,999 19,998 29,998 ‘39,997 62.5 20 1.250 62.5013 62.4988 0.6400 24,999 49,998 74,998 99,997 接收和发送缓冲器 接收和发送缓冲器,即FIFO,是千兆位级收发器的主要数字接口。FIFO通常是数据写入和 读出的地方。发送端通常有一个小型的FIFO,它要求读取和写入的时钟是等时同步 (isochronous)的(频率匹配但相位不一定匹配)。 38·XILINX

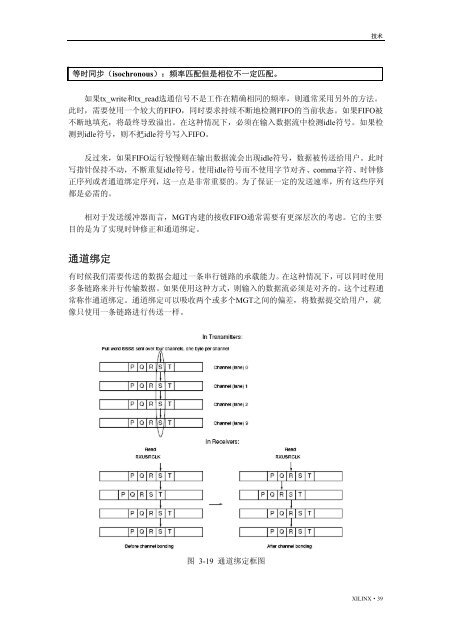

等时同步(isochronous):频率匹配但是相位不一定匹配。 如果tx_write和tx_read选通信号不是工作在精确相同的频率,则通常采用另外的方法。 此时,需要使用一个较大的FIFO,同时要求持续不断地检测FIFO的当前状态。如果FIFO被 不断地填充,将最终导致溢出。在这种情况下,必须在输入数据流中检测idle符号。如果检 测到idle符号,则不把idle符号写入FIFO。 反过来,如果FIFO运行较慢则在输出数据流会出现idle符号,数据被传送给用户。此时 写指针保持不动,不断重复idle符号。使用idle符号而不使用字节对齐、comma字符、时钟修 正序列或者通道绑定序列,这一点是非常重要的。为了保证一定的发送速率,所有这些序列 都是必需的。 相对于发送缓冲器而言,MGT内建的接收FIFO通常需要有更深层次的考虑。它的主要 目的是为了实现时钟修正和通道绑定。 通道绑定 有时候我们需要传送的数据会超过一条串行链路的承载能力。在这种情况下,可以同时使用 多条链路来并行传输数据。如果使用这种方式,则输入的数据流必须是对齐的。这个过程通 常称作通道绑定。通道绑定可以吸收两个或多个MGT之间的偏差,将数据提交给用户,就 像只使用一条链路进行传送一样。 图 3-19 通道绑定框图 技术 XILINX·39