轻松实现高速串行I/O

轻松实现高速串行I/O

轻松实现高速串行I/O

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

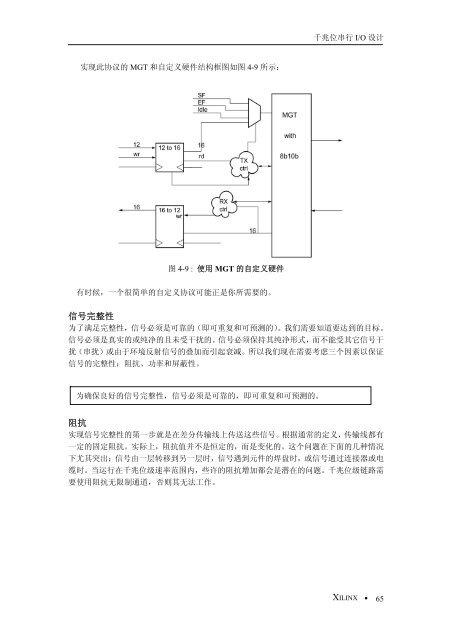

实现此协议的 MGT 和自定义硬件结构框图如图 4-9 所示:<br />

图 4-9 : 使用 MGT 的自定义硬件<br />

有时候,一个很简单的自定义协议可能正是你所需要的。<br />

千兆位串行 I/O 设计<br />

信号完整性<br />

为了满足完整性,信号必须是可靠的(即可重复和可预测的)。我们需要知道要达到的目标。<br />

信号必须是真实的或纯净的且未受干扰的。信号必须保持其纯净形式,而不能受其它信号干<br />

扰(串扰)或由于环境反射信号的叠加而引起衰减。所以我们现在需要考虑三个因素以保证<br />

信号的完整性:阻抗、功率和屏蔽性。<br />

为确保良好的信号完整性,信号必须是可靠的,即可重复和可预测的。<br />

阻抗<br />

实现信号完整性的第一步就是在差分传输线上传送这些信号。根据通常的定义,传输线都有<br />

一定的固定阻抗。实际上,阻抗值并不是恒定的,而是变化的。这个问题在下面的几种情况<br />

下尤其突出:信号由一层转移到另一层时,信号遇到元件的焊盘时,或信号通过连接器或电<br />

缆时。当运行在千兆位级速率范围内,些许的阻抗增加都会是潜在的问题。千兆位级链路需<br />

要使用阻抗无限制通道,否则其无法工作。<br />

XILINX • 65