轻松实现高速串行I/O

轻松实现高速串行I/O

轻松实现高速串行I/O

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

高速链路的问题和解决方案<br />

两种不同的 FPGA –TO-FPGA 数据链路的比较<br />

我并没有说 MGT 设计是不会遇到问题的。可能出现的问题包括工具问题、文档问题和其他一<br />

些意料不到的问题。但是,因为我们已经有所准备,所以我们在开发过程中可以很快地适应<br />

并解决这些问题。<br />

差分 BREF 时钟引脚<br />

就在我们要订制原材料板之前,发生了一件意料不到的事情,已经完成的板设计被暂时<br />

搁置。我的 Xilinx FAE 打电话告诉我们如果希望运行在 3.2Gb/s,我们必须注意特殊的时<br />

钟引脚。显然,这里面包括直接进入 MGT 的特殊低偏差时钟(BREFCLK)。问题是我们中没有<br />

人知道哪些引脚由 BREFCLK 提供时钟的。我们的设计因此搁置了两天,这两天里我们沿着神<br />

秘的 BREF 时钟引脚进行了追踪。<br />

我们最终确定了 BREF 的引脚数,但是 BREF 的问题并没有就此结束。BREF 引脚很难识<br />

别,因为 Xilinx 认为这些引脚是不需要的。实际上,Xilinx 已经从最初版本的 Virtex-II Pro<br />

FPGA 支持工具中删除了针对 BREF 通道的支持。幸运的是,还保留了一个插件,但是这个插<br />

件和多数 EDA 插件不同。除了运行脚本,在每次检查 PAR 时都需要不断的在 FPGA 编辑器上<br />

点击。虽然最后我们还是解决了这个问题,但是我们多少会有点失望。<br />

混乱的文档<br />

混乱的文档起初确实让我们有点失望。尽管如此,最混乱的还是时钟修正和<br />

comma/“K”字符问题。这些问题多数并不是错误,但是,其措词确实是十分混乱的。<br />

参数管理<br />

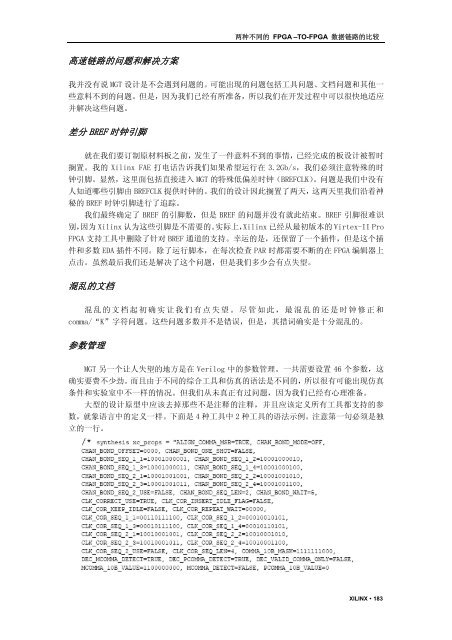

MGT 另一个让人失望的地方是在 Verilog 中的参数管理。一共需要设置 46 个参数,这<br />

确实要费不少劲。而且由于不同的综合工具和仿真的语法是不同的,所以很有可能出现仿真<br />

条件和实验室中不一样的情况。但我们从未真正有过问题,因为我们已经有心理准备。<br />

大型的设计原型中应该去掉那些不是注释的注释,并且应该定义所有工具都支持的参<br />

数,就象语言中的定义一样。下面是 4 种工具中 2 种工具的语法示例。注意第一句必须是独<br />

立的一行。<br />

XILINX·183