轻松实现高速串行I/O

轻松实现高速串行I/O

轻松实现高速串行I/O

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

基本工作原理和总体框图<br />

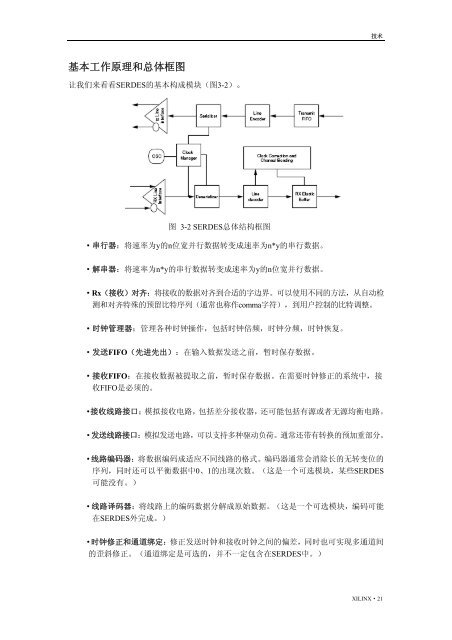

让我们来看看SERDES的基本构成模块(图3-2)。<br />

图 3-2 SERDES总体结构框图<br />

·串行器:将速率为y的n位宽并行数据转变成速率为n*y的串行数据。<br />

·解串器:将速率为n*y的串行数据转变成速率为y的n位宽并行数据。<br />

·Rx(接收)对齐:将接收的数据对齐到合适的字边界。可以使用不同的方法,从自动检<br />

测和对齐特殊的预留比特序列(通常也称作comma字符),到用户控制的比特调整。<br />

·时钟管理器:管理各种时钟操作,包括时钟倍频,时钟分频,时钟恢复。<br />

·发送FIFO(先进先出):在输入数据发送之前,暂时保存数据。<br />

·接收FIFO:在接收数据被提取之前,暂时保存数据。在需要时钟修正的系统中,接<br />

收FIFO是必须的。<br />

·接收线路接口:模拟接收电路,包括差分接收器,还可能包括有源或者无源均衡电路。<br />

·发送线路接口:模拟发送电路,可以支持多种驱动负荷。通常还带有转换的预加重部分。<br />

·线路编码器:将数据编码成适应不同线路的格式。编码器通常会消除长的无转变位的<br />

序列,同时还可以平衡数据中0、1的出现次数。(这是一个可选模块,某些SERDES<br />

可能没有。)<br />

·线路译码器:将线路上的编码数据分解成原始数据。(这是一个可选模块,编码可能<br />

在SERDES外完成。)<br />

·时钟修正和通道绑定:修正发送时钟和接收时钟之间的偏差,同时也可实现多通道间<br />

的歪斜修正。(通道绑定是可选的,并不一定包含在SERDES中。)<br />

技术<br />

XILINX·21