轻松实现高速串行I/O

轻松实现高速串行I/O

轻松实现高速串行I/O

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

介绍<br />

并行技术竭力适应新的接口需求。随着对特殊信令越来越多的需求,PCI 33之类的标准也发展<br />

成PCI 66。目前,低摆幅标准(如高速晶体管逻辑(HSTL))试图支持并行技术。同时,以太<br />

网速率从10Mb/s提高到100Mb/s,进而达到1000Mb/s。这类速度使得以太网非常适于应用在桌上<br />

型电脑中。<br />

这时,分数相位检测器(fractional phase detector)面世了。这项技术将串行接口速度提高到了<br />

千兆位级的范围。串行技术被证明是快速而功能强大的,可作为背板技术采用。随着串行引脚<br />

数和同步开关输出(SSO)的提高,千兆位级串行技术在PCB中获得了主导地位,取代了并行<br />

技术。<br />

基本I/O概念<br />

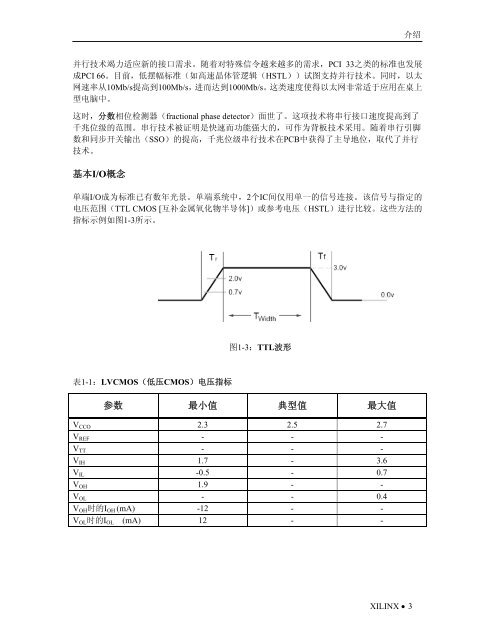

单端I/O成为标准已有数年光景。单端系统中,2个IC间仅用单一的信号连接。该信号与指定的<br />

电压范围(TTL CMOS [互补金属氧化物半导体])或参考电压(HSTL)进行比较。这些方法的<br />

指标示例如图1-3所示。<br />

表1-1:LVCMOS(低压CMOS)电压指标<br />

图1-3:TTL波形<br />

参数 最小值 典型值 最大值<br />

VCCO 2.3 2.5 2.7<br />

VREF - - -<br />

VTT - - -<br />

VIH 1.7 - 3.6<br />

VIL -0.5 - 0.7<br />

VOH 1.9 - -<br />

VOL - - 0.4<br />

VOH时的IOH (mA) -12 - -<br />

VOL时的IOL (mA) 12 - -<br />

XILINX • 3