轻松实现高速串行I/O

轻松实现高速串行I/O

轻松实现高速串行I/O

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

轻松实现高速串行 I/O •<br />

材料选择<br />

FR-4 成为标准的板材料已经有很多年,同时其他不少可供选择的低耗材料也变得更容易获<br />

得了。大体的原则是:若线路长小于 20inch 且速度小于等于 3.125 Gb/s,那么 FR-4 是可以<br />

接受的。如果我们需要更长的线路或者更高的速度,则我们应该认真考虑选用高速材料,例<br />

如 ROGERS 3450。<br />

叠层结构/板厚度<br />

一旦我们选定了材料,下一步就是制定一个总体的叠层结构设计。信号层数是固定的,叠层<br />

结构是可以改变的,但是我们在设计过程中应谨记所使用的叠层结构。同时不要忘了尽量让<br />

电源层和地层靠近以改善旁路的效果。<br />

电源层和地层<br />

我们需要考虑如何分配那些特殊的模拟电压值。所以我们可能会考虑为每个模拟<br />

电压值各自独立分配一层。隔离和滤波作为千兆位级信号参考层的地层可能会是<br />

个不错的主意。同时,在速度低于吉比特的信号区域,我们可以考虑省去数字电<br />

源层。<br />

差分线路对<br />

为了达到最好的效果,差分线路对应当紧密耦合并且接近匹配。线路长度匹配是极为必要<br />

的。在 FR-4 中,100mil(inch 的十分之一)的线路距离差会导致差分信号间有大约 18 皮秒<br />

的差异。这个偏差量足以引起问题。而且,就算我们使用普通的布线方法从一个 BGA 连接<br />

到另一个 BGA 时,十分之一英寸听起来都是很多的,但是往往差分线路对之间的长度差值<br />

可以达到 300-400mil。所以如果 PCB 工具中有自动线路匹配,我们最好使用它进行匹配。<br />

总体来说,我们希望差分线路对之间的长度差为 50mil 或者更小。<br />

差分线路宽度和间隔<br />

每种特定叠层结构都需要独自设计差分线路宽度和间隔。PCB 板制作厂家可以是一个非常<br />

有用的资源,但是我们要确保他们知道正在做什么。在一些发表的指导资料中,不建议让<br />

PCB 制作厂家来进行这些计算。我们需要确保厂家使用 filed solver 工具来表示紧密耦合的<br />

线路对的宽度和间隔。注意有一种技术我们绝对不能使用,即只选定几何结构而让 PCB 板<br />

制作厂家通过欠蚀刻和过蚀刻来调整阻抗。如果我们自己有自己的域解决软件并且可以熟练<br />

使用,那样会更好些。<br />

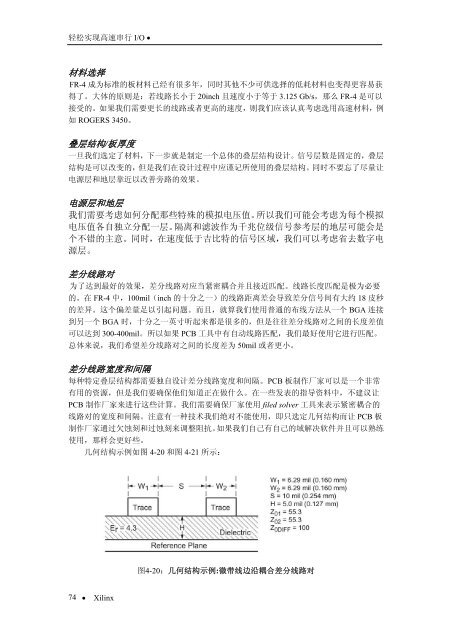

几何结构示例如图 4-20 和图 4-21 所示:<br />

74<br />

• Xilinx<br />

图4-20:几何结构示例:微带线边沿耦合差分线路对