轻松实现高速串行I/O

轻松实现高速串行I/O

轻松实现高速串行I/O

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

两种不同的 FPGA –TO-FPGA 数据链路的比较<br />

双倍数据速率的困惑<br />

我们在低速链路设计中还会遇到的一个问题是:需要涉及时钟的两个边沿。多位的 DDR 很难<br />

调试,因为数据通常是混合、交叉和令人困惑的。<br />

时钟传送_双倍数据速率发送器<br />

整体来说,发送器是设计中比较简单的部分。其结构基本就是标准的 DDR 输出。发送器的主<br />

要问题是数据和时钟的相位调整。我们最初计划是使传送时钟的相位和数据相差 90 度(图<br />

1-5)。这样时钟边沿会出现在数据稳定的区域内。<br />

图 1-5 异相的时钟和数据<br />

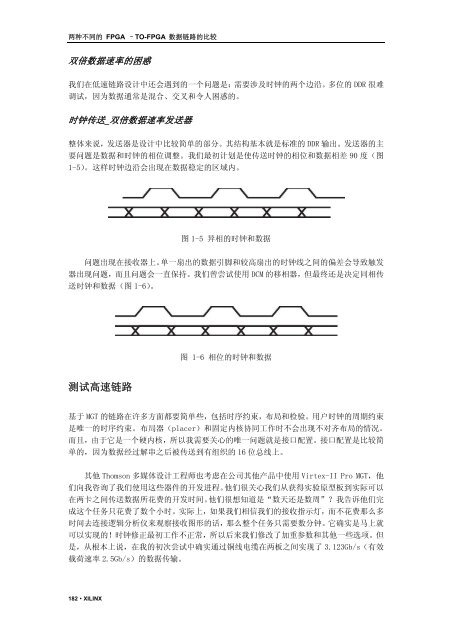

问题出现在接收器上。单一扇出的数据引脚和较高扇出的时钟线之间的偏差会导致触发<br />

器出现问题,而且问题会一直保持。我们曾尝试使用 DCM 的移相器,但最终还是决定同相传<br />

送时钟和数据(图 1-6)。<br />

测试高速链路<br />

图 1-6 相位的时钟和数据<br />

基于 MGT 的链路在许多方面都要简单些,包括时序约束,布局和检验。用户时钟的周期约束<br />

是唯一的时序约束。布局器(placer)和固定内核协同工作时不会出现不对齐布局的情况。<br />

而且,由于它是一个硬内核,所以我需要关心的唯一问题就是接口配置。接口配置是比较简<br />

单的,因为数据经过解串之后被传送到有组织的 16 位总线上。<br />

其他 Thomson 多媒体设计工程师也考虑在公司其他产品中使用 Virtex-II Pro MGT,他<br />

们向我咨询了我们使用这些器件的开发进程。他们很关心我们从获得实验原型板到实际可以<br />

在两卡之间传送数据所花费的开发时间。他们很想知道是“数天还是数周”?我告诉他们完<br />

成这个任务只花费了数个小时。实际上,如果我们相信我们的接收指示灯,而不花费那么多<br />

时间去连接逻辑分析仪来观察接收图形的话,那么整个任务只需要数分钟。它确实是马上就<br />

可以实现的!时钟修正最初工作不正常,所以后来我们修改了加重参数和其他一些选项。但<br />

是,从根本上说,在我的初次尝试中确实通过铜线电缆在两板之间实现了 3.123Gb/s(有效<br />

载荷速率 2.5Gb/s)的数据传输。<br />

182·XILINX