轻松实现高速串行I/O

轻松实现高速串行I/O

轻松实现高速串行I/O

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

两种不同的 FPGA –TO-FPGA 数据链路的比较<br />

局部时钟<br />

我们不能使用全局时钟资源、全局缓存(BUFG)或 DCM 来作为伴随数据传送的时钟,因为我<br />

们在单个 FPGA 中需要 19 条低速链路。局部时钟安排不合理是导致原型失败的真正原因。<br />

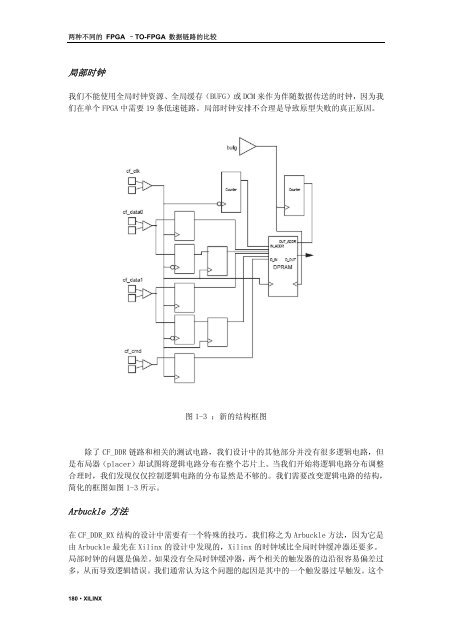

图 1-3 :新的结构框图<br />

除了 CF_DDR 链路和相关的测试电路,我们设计中的其他部分并没有很多逻辑电路,但<br />

是布局器(placer)却试图将逻辑电路分布在整个芯片上。当我们开始将逻辑电路分布调整<br />

合理时,我们发现仅仅控制逻辑电路的分布显然是不够的。我们需要改变逻辑电路的结构,<br />

简化的框图如图 1-3 所示。<br />

Arbuckle 方法<br />

在 CF_DDR_RX 结构的设计中需要有一个特殊的技巧。我们称之为 Arbuckle 方法,因为它是<br />

由 Arbuckle 最先在 Xilinx 的设计中发现的,Xilinx 的时钟域比全局时钟缓冲器还要多。<br />

局部时钟的问题是偏差。如果没有全局时钟缓冲器,两个相关的触发器的边沿很容易偏差过<br />

多,从而导致逻辑错误。我们通常认为这个问题的起因是其中的一个触发器过早触发。这个<br />

180·XILINX