轻松实现高速串行I/O

轻松实现高速串行I/O

轻松实现高速串行I/O

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

图 4-36: MGT 仿真<br />

千兆位串行 I/O 设计<br />

仿真的时标(time scale)必须不断调整,这会使事情变得更慢。甚至在屏幕上重绘这些<br />

信号也会显著变慢。我们可以通过下面几项措施来减小影响。首先我们必须清楚地认识到速<br />

度必将会是一个问题,并且围绕着“这些高速信号是设计的一部分”这个事实来不断优化我<br />

们的仿真。另一件必须要记住的事情是许多 MGT 模型都有一个并行的输入和输出端口。如<br />

果我们在大多数的测试台中使用这些措施,并创建一个实际运行在全数据速率的小型测试组<br />

件,则 MGT 对全局验证时间的影响将会大大减小。这种方法的框图如图 4-37 所示。<br />

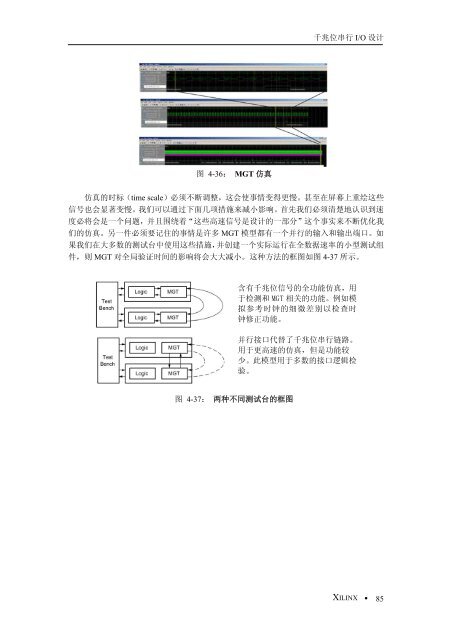

图 4-37: 两种不同测试台的框图<br />

含有千兆位信号的全功能仿真,用<br />

于检测和 MGT 相关的功能。例如模<br />

拟参考时钟的细微差别以检查时<br />

钟修正功能。<br />

并行接口代替了千兆位串行链路。<br />

用于更高速的仿真,但是功能较<br />

少。此模型用于多数的接口逻辑检<br />

验。<br />

XILINX • 85