×

Your ePaper is waiting for publication!

By publishing your document, the content will be optimally indexed by Google via AI and sorted into the right category for over 500 million ePaper readers on YUMPU.

This will ensure high visibility and many readers!

PUBLISH DOCUMENT

No, I renounce more range.

You can find your publication here:

Share your interactive ePaper on all platforms and on your website with our embed function

⬤

⬤

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

轻松实现高速串行 I/O •<br />

源同步<br />

6<br />

• XILINX<br />

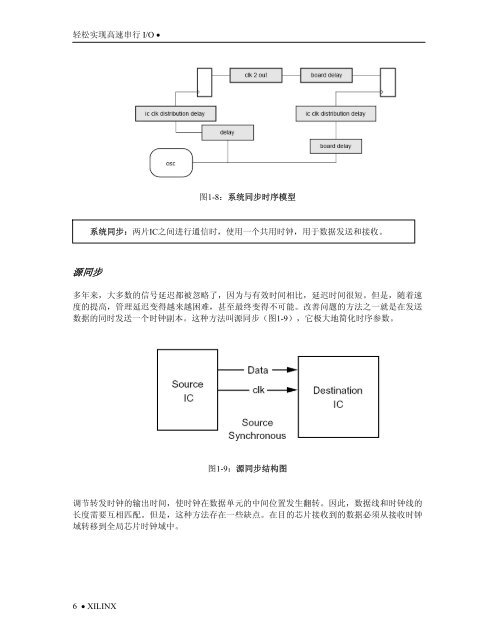

图1-8:系统同步时序模型<br />

系统同步:两片IC之间进行通信时,使用一个共用时钟,用于数据发送和接收。<br />

多年来,大多数的信号延迟都被忽略了,因为与有效时间相比,延迟时间很短。但是,随着速<br />

度的提高,管理延迟变得越来越困难,甚至最终变得不可能。改善问题的方法之一就是在发送<br />

数据的同时发送一个时钟副本。这种方法叫源同步(图1-9),它极大地简化时序参数。<br />

图1-9:源同步结构图<br />

调节转发时钟的输出时间,使时钟在数据单元的中间位置发生翻转。因此,数据线和时钟线的<br />

长度需要互相匹配。但是,这种方法存在一些缺点。在目的芯片接收到的数据必须从接收时钟<br />

域转移到全局芯片时钟域中。

轻松实现高速串行 I/O • 源同步 6 • XILINX 图1-8:系统同步时序模型 系统同步:两片IC之间进行通信时,使用一个共用时钟,用于数据发送和接收。 多年来,大多数的信号延迟都被忽略了,因为与有效时间相比,延迟时间很短。但是,随着速 度的提高,管理延迟变得越来越困难,甚至最终变得不可能。改善问题的方法之一就是在发送 数据的同时发送一个时钟副本。这种方法叫源同步(图1-9),它极大地简化时序参数。 图1-9:源同步结构图 调节转发时钟的输出时间,使时钟在数据单元的中间位置发生翻转。因此,数据线和时钟线的 长度需要互相匹配。但是,这种方法存在一些缺点。在目的芯片接收到的数据必须从接收时钟 域转移到全局芯片时钟域中。

图1-10:源同步时序模型 介绍 源同步:两个IC间进行通信时,发送IC生成一个伴随发送数据的时钟信号。接收IC利用该转 发时钟进行数据接收。 转发时钟:转发时钟(cf)或时钟转发是用于源同步的另一个技术术语。 源同步设计导致时钟域数量的剧增。对于具有有限时钟缓冲器的现场可编程门阵列(FPGA)和 必须量身定制每个时钟树的专用集成电路(ASIC)等器件来说,这将带来时序约束和分析难题。 对于采用大型并行总线的设计来说,该问题会进一步加重:由于电路板的设计限制,每条数据 总线通常需要采用1个以上的转发时钟。因此,一条32位总线可能需要4个、甚至是8个转发时钟。 自同步 自同步模型如图1-11所示。这里,数据流包含数据和时钟。 图1-11:自同步结构图 XILINX • 7

Page 1 and 2: 连接功能解决方案 1.0版 轻 Page 3 and 4: 轻松实现高速串行 I/O © 200 Page 5 and 6: 轻松实现高速串行 I/O iv Page 7 and 8: 轻松实现高速串行 I/O vi Xi Page 9 and 10: 轻松实现高速串行 I/O viii Page 11 and 12: 轻松实现高速串行 I/O 技巧 Page 13 and 14: 第一章 介绍 数字I/O信号处 Page 15 and 16: 介绍 并行技术竭力适应新 Page 17: 介绍 随着IC通信速度的提 Page 21 and 22: 串并转换 串并转换与并串 Page 23 and 24: 第二章 为何需要千兆位串 Page 25 and 26: 图2-2:采用解串行化和串行 Page 27 and 28: 表2-1给出了2种方式下所需 Page 29 and 30: 板到板/背板 为何需要千兆 Page 31 and 32: 第三章 技术 实现千兆位串 Page 33 and 34: 基本工作原理和总体框图 Page 35 and 36: 为何SERDES速度如此之快? 图 Page 37 and 38: 图3-6 多重相位提取电路的 Page 39 and 40: 控制字符 表 3-3列出了12个 Page 41 and 42: K表示控制字符。3位转化为 Page 43 and 44: 通常,因为存在不允许的数 Page 45 and 46: 常用的0位宽符号是t(结尾) Page 47 and 48: 低开销的代价是更长的对 Page 49 and 50: 图3-18给出了一些最新发布 Page 51 and 52: 等时同步(isochronous):频率匹 Page 53 and 54: 图3-20给出了一个CML型的驱 Page 55 and 56: 如果串行流包含多个比特 Page 57 and 58: 眼图:数字采样示波器上通 Page 59 and 60: 如果给定线路的长度以及 Page 61 and 62: 图 3-35 均衡系统频率响应 Page 63 and 64: 一些高端电缆有均衡化的 Page 65 and 66: 主要有三个原因: 1. 宇宙射 Page 67 and 68: SERDES 技术促进 I/O 设计的 Page 69 and 70: 轻松实现高速串行 I/O •

Page 71 and 72: 轻松实现高速串行 I/O • PI

Page 73 and 74: 轻松实现高速串行 I/O •

Page 75 and 76: 轻松实现高速串行 I/O •

Page 77 and 78: 轻松实现高速串行 I/O • TD

Page 79 and 80: 轻松实现高速串行 I/O • 68

Page 81 and 82: 轻松实现高速串行 I/O • ES

Page 83 and 84: 轻松实现高速串行 I/O •

Page 85 and 86: 轻松实现高速串行 I/O •

Page 87 and 88: 轻松实现高速串行 I/O •

Page 89 and 90: 轻松实现高速串行 I/O •

Page 91 and 92: 轻松实现高速串行 I/O •

Page 93 and 94: 轻松实现高速串行 I/O •

Page 95 and 96: 轻松实现高速串行 I/O •

Page 97 and 98: 轻松实现高速串行 I/O •

Page 99 and 100: 轻松实现高速串行 I/O • 88

Page 101 and 102: 轻松实现高速串行 I/O •

Page 103 and 104: 轻松实现高速串行 I/O •

Page 105 and 106: 轻松实现高速串行 I/O •

Page 107 and 108: 轻松实现高速串行 I/O •

Page 109 and 110: 轻松实现高速串行 I/O •

Page 111 and 112: 轻松实现高速串行 I/O •

Page 113 and 114: 第5章 Xilinx—您的设计合作

Page 115 and 116: 信号完整性中心 XILINX—您

Page 117 and 118: Xilinx—强大的设计合作伙

Page 119 and 120: 附录 A SERDES 示例资料 ——

Page 121 and 122: SERDES 示例资料—RocketIO X

Page 123 and 124: 可用端口 SERDES 示例资料—

Page 125 and 126: SERDES 示例资料—RocketIO X

Page 127 and 128: SERDES 示例资料—RocketIO X

Page 129 and 130: 表1-4 设计原型端口(续) 输

Page 131 and 132: 表1-5 RocketIO X 收发器属性(

Page 133 and 134: 表1-5 RocketIO X 收发器属性(

Page 135 and 136: 表1-5 RocketIO X 收发器属性(

Page 137 and 138: 和数据位 TXDATA[7:0]相关联

Page 139 and 140: 接收结构 SERDES 示例资料—

Page 141 and 142: ·POWERDOWN ·RXRESET ·TXRESET S

Page 143 and 144: 表1-10 数据宽度,时钟比例(

Page 145 and 146: SERDES 示例资料—RocketIO X

Page 147 and 148: TXCHARISK SERDES 示例资料—Roc

Page 149 and 150: SERDES 示例资料—RocketIO X

Page 151 and 152: SERDES 示例资料—RocketIO X

Page 153 and 154: 表1-15 数据对齐(续) ENMCOMMAA

Page 155 and 156: 表1-17 发送端64b/66b编码器

Page 157 and 158: G(x) = 1 + x39 + x58 SERDES 示例

Page 159 and 160: 图1-11 块同步状态机 SERDES

Page 161 and 162: 时钟修正序列 SERDES 示例资

Page 163 and 164: 01020304 05060708 000000FF 01020304

Page 165 and 166: SERDES 示例资料—RocketIO X

Page 167 and 168: 事件指示 SERDES 示例资料—

Page 169 and 170: SERDES 示例资料—RocketIO X

Page 171 and 172: 附录 B 8b/10b 列表 本信息来

Page 173 and 174: 表1-1: 有效数据字符(续) 数

Page 175 and 176: 表1-1: 有效数据字符(续) 数

Page 177 and 178: 表1-1: 有效数据字符(续) 数

Page 179 and 180: 表1-1: 有效数据字符(续) 数

Page 181 and 182: 表1-1: 有效数据字符(续) 数

Page 183 and 184: 附录 C 两种不同的 FPGA-to-FP

Page 185 and 186: 两种不同的 FPGA -TO-FPGA 数

Page 187 and 188: 两种不同的 FPGA -TO-FPGA 数

Page 189 and 190: 两种不同的 FPGA -TO-FPGA 数

Page 191 and 192: 两种不同的 FPGA -TO-FPGA 数

Page 193 and 194: 高速链路的问题和解决方

Page 195 and 196: 两种不同的 FPGA -TO-FPGA 数

Page 197 and 198: 附件D 术语表 术语表 4b/5b:

Page 199 and 200: 术语表 确定性抖动:由具体

Page 201 and 202: OC-192:光学载波192 (10 Gb/s). P

Page 203 and 204: 术语表 于印刷电路板表面

×

Inappropriate

Flag as Inappropriate

Cancel

×

Inappropriate

You have already flagged this document.

×

Mail this publication

Delete template?

Are you sure you want to delete your template?

×

DOWNLOAD ePAPER

This ePaper is currently not available for download.