轻松实现高速串行I/O

轻松实现高速串行I/O

轻松实现高速串行I/O

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

两种不同的 FPGA –TO-FPGA 数据链路的比较<br />

Xilinx 一开始并不能确保这种方法是可行的,因为他们只在仅带 2 个连接器的数英寸<br />

厚的 FR4 PC 板上进行了测试。不管怎样,Xilinx 告诉我如果我们希望尝试新的方案,他们<br />

也愿意进行测试。幸运的是,我有一个可用的解决方案—当时有一些工业界最优秀的高速信<br />

号操作工程师和我一起工作,而且他们可以设计我所需要的东西。他们在将高精确度的串行<br />

数字视频信号传输通过连接器、背板和电缆这方面已经有多年的经验。但是这些信号的速率<br />

只有 1.5Gb/s,所以还是会有潜在的长时间的无切换时隙。频谱通常被有趣地称作"DC to<br />

light",它是个外表令人讨厌的信号。我需要使用更高的速率以及由 8b/10b 编码/解码提供<br />

的有保证转换。我的高速工程专家们很有信心可以让电缆和连接器工作得相当完美,但是他<br />

们很担心数字噪声会进入模拟电路。现在看来值得庆幸的是,我们最终决定尝试这种方法。<br />

实现细节<br />

系统结构已经就位,现在应该开始写 Verilog HDL 来实现我们的硬件设计。<br />

低速链路<br />

CF_DDR 链路的编程并不是相当困难的,但是也不像我们所预期的那么容易。我们一开始计<br />

划使用 Xilinx 网站上的参考设计作为起点,但是参考设计使用的是结构化设计原型而不是<br />

行为描述方法。我们不想去实例化设计原型,而且我们懂得寄存器传输语言(Register<br />

Transfer Language,RTL)Verilog,同时能够使用工具调通程序。<br />

随着设计的开始,问题开始增加。我们怎样保证输入/输出块(IOB)的 DDR 功能的使用?<br />

怎样才能使 LVDS I/O 标准适用?不同综合工具的方法可能会稍有不同。<br />

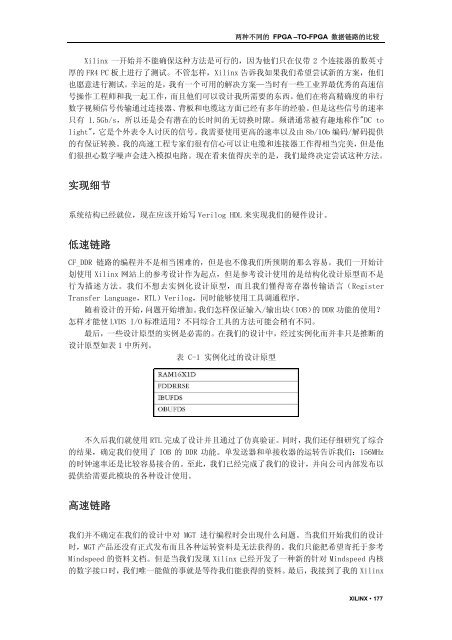

最后,一些设计原型的实例是必需的。在我们的设计中,经过实例化而并非只是推断的<br />

设计原型如表 1 中所列。<br />

表 C-1 实例化过的设计原型<br />

不久后我们就使用 RTL 完成了设计并且通过了仿真验证。同时,我们还仔细研究了综合<br />

的结果,确定我们使用了 IOB 的 DDR 功能。单发送器和单接收器的运转告诉我们:156MHz<br />

的时钟速率还是比较容易接合的。至此,我们已经完成了我们的设计,并向公司内部发布以<br />

提供给需要此模块的各种设计使用。<br />

高速链路<br />

我们并不确定在我们的设计中对 MGT 进行编程时会出现什么问题。当我们开始我们的设计<br />

时,MGT 产品还没有正式发布而且各种运转资料是无法获得的。我们只能把希望寄托于参考<br />

Mindspeed 的资料文档。但是当我们发现 Xilinx 已经开发了一种新的针对 Mindspeed 内核<br />

的数字接口时,我们唯一能做的事就是等待我们能获得的资料。最后,我接到了我的 Xilinx<br />

XILINX·177