PDF-Ausgabe herunterladen (34.2 MB) - elektronik industrie

PDF-Ausgabe herunterladen (34.2 MB) - elektronik industrie

PDF-Ausgabe herunterladen (34.2 MB) - elektronik industrie

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

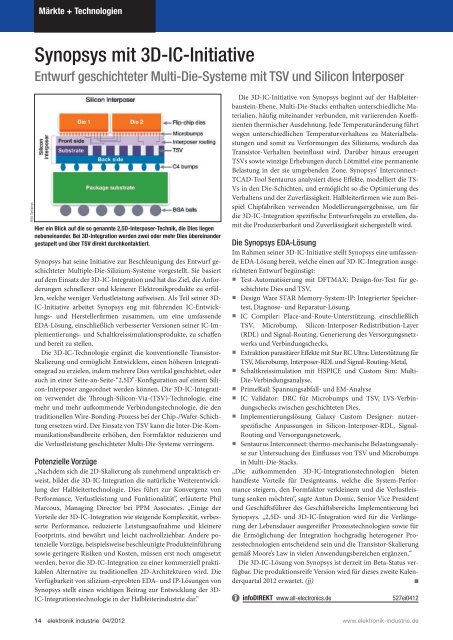

Märkte + TechnologienSynopsys mit 3D-IC-InitiativeEntwurf geschichteter Multi-Die-Systeme mit TSV und Silicon InterposerBild: SynopsysHier ein Blick auf die so genannte 2,5D-Interposer-Technik, die Dies liegennebeneinander. Bei 3D-Integration werden zwei oder mehr Dies übereinandergestapelt und über TSV direkt durchkontaktiert.Synopsys hat seine Initiative zur Beschleunigung des Entwurf geschichteterMultiple-Die-Silizium-Systeme vorgestellt. Sie basiertauf dem Einsatz der 3D-IC-Integration und hat das Ziel, die Anforderungenschnellerer und kleinerer Elektronikprodukte zu erfüllen,welche weniger Verlustleistung aufweisen. Als Teil seiner 3D-IC-Initiative arbeitet Synopsys eng mit führenden IC-Entwicklungs-und Herstellerfirmen zusammen, um eine umfassendeEDA-Lösung, einschließlich verbesserter Versionen seiner IC-Implementierungs-und Schaltkreissimulationsprodukte, zu schaffenund bereit zu stellen.Die 3D-IC-Technologie ergänzt die konventionelle Transistor-Skalierung und ermöglicht Entwicklern, einen höheren Integrationsgradzu erzielen, indem mehrere Dies vertikal geschichtet, oderauch in einer Seite-an-Seite-“2,5D”-Konfiguration auf einem Silicon-Interposerangeordnet werden können. Die 3D-IC-Integrationverwendet die Through-Silicon-Via-(TSV)-Technologie, einemehr und mehr aufkommende Verbindungstechnologie, die dentraditionellen Wire-Bonding-Prozess bei der Chip-/Wafer-Schichtungersetzen wird. Der Einsatz von TSV kann die Inter-Die-Kommunikationsbandbreiteerhöhen, den Formfaktor reduzieren unddie Verlustleistung geschichteter Multi-Die-Systeme verringern.Potenzielle Vorzüge„Nachdem sich die 2D-Skalierung als zunehmend unpraktisch erweist,bildet die 3D-IC-Integration die natürliche Weiterentwicklungder Halbleitertechnologie. Dies führt zur Konvergenz vonPerformance, Verlustleistung und Funktionalität”, erläuterte PhilMarcoux, Managing Director bei PPM Associates. „Einige derVorteile der 3D-IC-Integration wie steigende Komplexität, verbessertePerformance, reduzierte Leistungsaufnahme und kleinereFootprints, sind bewährt und leicht nachvollziehbar. Andere potenzielleVorzüge, beispielsweise beschleunigte Produkteinführungsowie geringere Risiken und Kosten, müssen erst noch umgesetztwerden, bevor die 3D-IC-Integration zu einer kommerziell praktikablenAlternative zu traditionellen 2D-Architekturen wird. DieVerfügbarkeit von silizium-erprobten EDA- und IP-Lösungen vonSynopsys stellt einen wichtigen Beitrag zur Entwicklung der 3D-IC-Integrationstechnologie in der Halbleiter<strong>industrie</strong> dar.”Die 3D-IC-Initiative von Synopsys beginnt auf der Halbleiterbaustein-Ebene.Multi-Die-Stacks enthalten unterschiedliche Materialien,häufig miteinander verbunden, mit variierenden Koeffiziententhermischer Ausdehnung. Jede Temperaturänderung führtwegen unterschiedlichen Temperaturverhaltens zu Materialbelastungenund somit zu Verformungen des Siliziums, wodurch dasTransistor-Verhalten beeinflusst wird. Darüber hinaus erzeugenTSVs sowie winzige Erhebungen durch Lötmittel eine permanenteBelastung in der sie umgebenden Zone. Synopsys’ Interconnect-TCAD-Tool Sentaurus analysiert diese Effekte, modelliert die TS-Vs in den Die-Schichten, und ermöglicht so die Optimierung desVerhaltens und der Zuverlässigkeit. Halbleiterfirmen wie zum BeispielChipfabriken verwenden Modellierungsergebnisse, um fürdie 3D-IC-Integration spezifische Entwurfsregeln zu erstellen, damitdie Produzierbarkeit und Zuverlässigkeit sichergestellt wird.Die Synopsys EDA-LösungIm Rahmen seiner 3D-IC-Initiative stellt Synopsys eine umfassendeEDA-Lösung bereit, welche einen auf 3D-IC-Integration ausgerichtetenEntwurf begünstigt:■■ Test-Automatisierung mit DFTMAX: Design-for-Test für geschichteteDies und TSV,■■ Design Ware STAR Memory-System-IP: Integrierter Speichertest,Diagnose- und Reparatur-Lösung,■■ IC Compiler: Place-and-Route-Unterstützung, einschließlichTSV, Microbump, Silicon-Interposer-Redistribution-Layer(RDL) und Signal-Routing, Generierung des Versorgungsnetzwerksund Verbindungschecks,■■ Extraktion parasitärer Effekte mit Star RC Ultra: Unterstützung fürTSV, Microbump, Interposer-RDL und Signal-Routing-Metal,■■ Schaltkreissimulation mit HSPICE und Custom Sim: Multi-Die-Verbindungsanalyse,■■ PrimeRail: Spannungsabfall- und EM-Analyse■■ IC Validator: DRC für Microbumps und TSV, LVS-Verbindungscheckszwischen geschichteten Dies,■■ Implementierungslösung Galaxy Custom Designer: nutzerspezifischeAnpassungen in Silicon-Interposer-RDL, Signal-Routing und Versorgungsnetzwerk,■■ Sentaurus Interconnect: thermo-mechanische Belastungsanalysezur Untersuchung des Einflusses von TSV und Microbumpsin Multi-Die-Stacks.„Die aufkommenden 3D-IC-Integrationstechnologien bietenhandfeste Vorteile für Designteams, welche die System-Performancesteigern, den Formfaktor verkleinern und die Verlustleistungsenken möchten”, sagte Antun Domic, Senior Vice Presidentund Geschäftsführer des Geschäftsbereichs Implementierung beiSynopsys. „2,5D- und 3D-IC-Integration wird für die Verlängerungder Lebensdauer ausgereifter Prozesstechnologien sowie fürdie Ermöglichung der Integration hochgradig heterogener Prozesstechnologienentscheidend sein und die Transistor-Skalierunggemäß Moore’s Law in vielen Anwendungsbereichen ergänzen.“Die 3D-IC-Lösung von Synopsys ist derzeit im Beta-Status verfügbar.Die produktionsreife Version wird für dieses zweite Kalenderquartal2012 erwartet. (jj)ninfoDIREKT www.all-electronics.de 527ei041214 <strong>elektronik</strong> <strong>industrie</strong> 04/2012www.<strong>elektronik</strong>-<strong>industrie</strong>.de