E200Z1RM, e200z1 Power Architecture Ž Core - Reference Manual

E200Z1RM, e200z1 Power Architecture Ž Core - Reference Manual

E200Z1RM, e200z1 Power Architecture Ž Core - Reference Manual

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

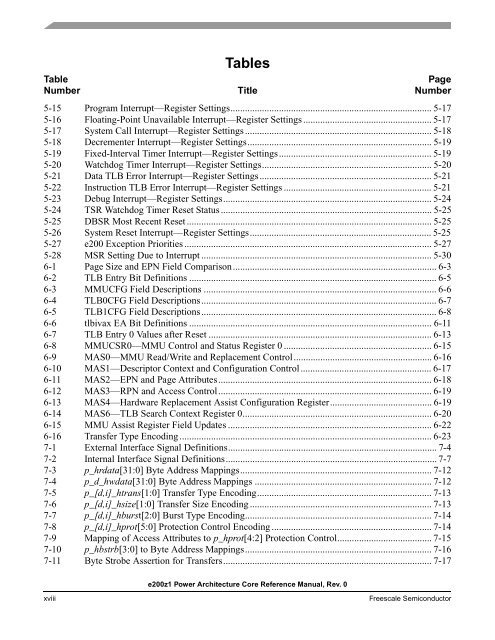

Tables<br />

Table<br />

Number Title<br />

<strong>e200z1</strong> <strong>Power</strong> <strong>Architecture</strong> <strong>Core</strong> <strong>Reference</strong> <strong>Manual</strong>, Rev. 0<br />

Page<br />

Number<br />

5-15 Program Interrupt—Register Settings................................................................................... 5-17<br />

5-16 Floating-Point Unavailable Interrupt—Register Settings..................................................... 5-17<br />

5-17 System Call Interrupt—Register Settings ............................................................................. 5-18<br />

5-18 Decrementer Interrupt—Register Settings............................................................................ 5-19<br />

5-19 Fixed-Interval Timer Interrupt—Register Settings............................................................... 5-19<br />

5-20 Watchdog Timer Interrupt—Register Settings...................................................................... 5-20<br />

5-21 Data TLB Error Interrupt—Register Settings....................................................................... 5-21<br />

5-22 Instruction TLB Error Interrupt—Register Settings ............................................................. 5-21<br />

5-23 Debug Interrupt—Register Settings...................................................................................... 5-24<br />

5-24 TSR Watchdog Timer Reset Status ....................................................................................... 5-25<br />

5-25 DBSR Most Recent Reset ..................................................................................................... 5-25<br />

5-26 System Reset Interrupt—Register Settings........................................................................... 5-25<br />

5-27 e200 Exception Priorities ...................................................................................................... 5-27<br />

5-28 MSR Setting Due to Interrupt ............................................................................................... 5-30<br />

6-1 Page Size and EPN Field Comparison.................................................................................... 6-3<br />

6-2 TLB Entry Bit Definitions ...................................................................................................... 6-5<br />

6-3 MMUCFG Field Descriptions ................................................................................................ 6-6<br />

6-4 TLB0CFG Field Descriptions................................................................................................. 6-7<br />

6-5 TLB1CFG Field Descriptions................................................................................................. 6-8<br />

6-6 tlbivax EA Bit Definitions .................................................................................................... 6-11<br />

6-7 TLB Entry 0 Values after Reset ............................................................................................ 6-13<br />

6-8 MMUCSR0—MMU Control and Status Register 0 ............................................................. 6-15<br />

6-9 MAS0—MMU Read/Write and Replacement Control......................................................... 6-16<br />

6-10 MAS1—Descriptor Context and Configuration Control...................................................... 6-17<br />

6-11 MAS2—EPN and Page Attributes........................................................................................ 6-18<br />

6-12 MAS3—RPN and Access Control........................................................................................ 6-19<br />

6-13 MAS4—Hardware Replacement Assist Configuration Register.......................................... 6-19<br />

6-14 MAS6—TLB Search Context Register 0.............................................................................. 6-20<br />

6-15 MMU Assist Register Field Updates .................................................................................... 6-22<br />

6-16 Transfer Type Encoding ........................................................................................................ 6-23<br />

7-1 External Interface Signal Definitions...................................................................................... 7-4<br />

7-2 Internal Interface Signal Definitions....................................................................................... 7-7<br />

7-3 p_hrdata[31:0] Byte Address Mappings............................................................................... 7-12<br />

7-4 p_d_hwdata[31:0] Byte Address Mappings ......................................................................... 7-12<br />

7-5 p_[d,i]_htrans[1:0] Transfer Type Encoding........................................................................ 7-13<br />

7-6 p_[d,i]_hsize[1:0] Transfer Size Encoding ........................................................................... 7-13<br />

7-7 p_[d,i]_hburst[2:0] Burst Type Encoding............................................................................. 7-14<br />

7-8 p_[d,i]_hprot[5:0] Protection Control Encoding .................................................................. 7-14<br />

7-9 Mapping of Access Attributes to p_hprot[4:2] Protection Control....................................... 7-15<br />

7-10 p_hbstrb[3:0] to Byte Address Mappings............................................................................. 7-16<br />

7-11 Byte Strobe Assertion for Transfers...................................................................................... 7-17<br />

xviii Freescale Semiconductor