MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>MAX9272</strong><br />

<strong>28</strong>-<strong>Bit</strong> <strong>GMSL</strong> <strong>Deserializer</strong> <strong>f<strong>or</strong></strong> <strong>Coax</strong> <strong>or</strong> <strong>STP</strong> <strong>Cable</strong><br />

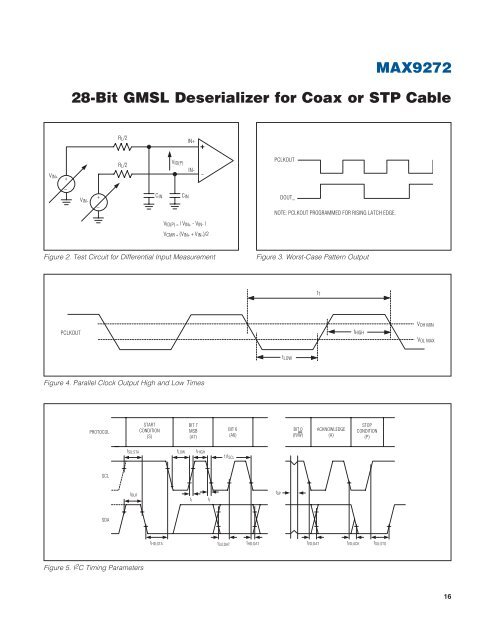

R L/2<br />

R L /2<br />

V IN+ +<br />

_<br />

+<br />

V IN-<br />

_<br />

IN+<br />

V ID(P)<br />

IN- _<br />

C IN C IN<br />

V ID(P) = | V IN+ - V IN- |<br />

V CMR = (V IN+ + V IN- )/2<br />

PCLKOUT<br />

DOUT_<br />

NOTE: PCLKOUT PROGRAMMED FOR RISING LATCH EDGE.<br />

Figure 2. Test Circuit <strong>f<strong>or</strong></strong> Differential Input Measurement<br />

Figure 3. W<strong>or</strong>st-Case Pattern Output<br />

PCLKOUT<br />

t T<br />

V OH MIN<br />

t HIGH<br />

V OL MAX<br />

t LOW<br />

Figure 4. Parallel Clock Output High and Low Times<br />

PROTOCOL<br />

START<br />

CONDITION<br />

(S)<br />

BIT 7<br />

MSB<br />

(A7)<br />

BIT 6<br />

(A6)<br />

BIT 0<br />

(R/W)<br />

ACKNOWLEDGE<br />

(A)<br />

STOP<br />

CONDITION<br />

(P)<br />

t SU;STA t LOW<br />

t SP<br />

t HIGH<br />

1/f SCL<br />

SCL<br />

t BUF<br />

t HD;STA<br />

t r t f<br />

t SU;DAT t HD;DAT t VD;DAT t VD;ACK t SU;STO<br />

SDA<br />

Figure 5. I 2 C Timing Parameters<br />

16

![P-CAD EDA - [Sheet1]](https://img.yumpu.com/49470492/1/190x115/p-cad-eda-sheet1.jpg?quality=85)