MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>MAX9272</strong><br />

<strong>28</strong>-<strong>Bit</strong> <strong>GMSL</strong> <strong>Deserializer</strong> <strong>f<strong>or</strong></strong> <strong>Coax</strong> <strong>or</strong> <strong>STP</strong> <strong>Cable</strong><br />

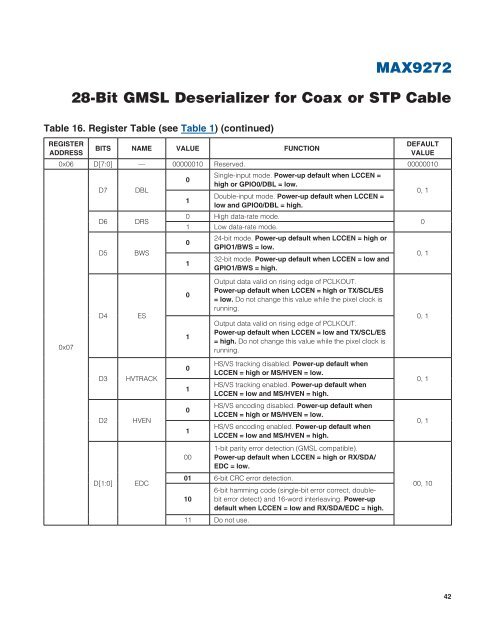

Table 16. Register Table (see Table 1) (continued)<br />

REGISTER<br />

ADDRESS<br />

BITS NAME VALUE FUNCTION<br />

DEFAULT<br />

VALUE<br />

0x06 D[7:0] — 00000010 Reserved. 00000010<br />

D7<br />

D6<br />

D5<br />

DBL<br />

DRS<br />

BWS<br />

0<br />

1<br />

Single-input mode. Power-up default when LCCEN =<br />

high <strong>or</strong> GPIO0/DBL = low.<br />

Double-input mode. Power-up default when LCCEN =<br />

low and GPIO0/DBL = high.<br />

0 High data-rate mode.<br />

1 Low data-rate mode.<br />

0<br />

1<br />

24-bit mode. Power-up default when LCCEN = high <strong>or</strong><br />

GPIO1/BWS = low.<br />

32-bit mode. Power-up default when LCCEN = low and<br />

GPIO1/BWS = high.<br />

0, 1<br />

0<br />

0, 1<br />

0x07<br />

D4<br />

ES<br />

0<br />

1<br />

Output data valid on rising edge of PCLKOUT.<br />

Power-up default when LCCEN = high <strong>or</strong> TX/SCL/ES<br />

= low. Do not change this value while the pixel clock is<br />

running.<br />

Output data valid on rising edge of PCLKOUT.<br />

Power-up default when LCCEN = low and TX/SCL/ES<br />

= high. Do not change this value while the pixel clock is<br />

running.<br />

0, 1<br />

D3<br />

HVTRACK<br />

0<br />

1<br />

HS/VS tracking disabled. Power-up default when<br />

LCCEN = high <strong>or</strong> MS/HVEN = low.<br />

HS/VS tracking enabled. Power-up default when<br />

LCCEN = low and MS/HVEN = high.<br />

0, 1<br />

D2<br />

HVEN<br />

0<br />

1<br />

HS/VS encoding disabled. Power-up default when<br />

LCCEN = high <strong>or</strong> MS/HVEN = low.<br />

HS/VS encoding enabled. Power-up default when<br />

LCCEN = low and MS/HVEN = high.<br />

0, 1<br />

00<br />

1-bit parity err<strong>or</strong> detection (<strong>GMSL</strong> compatible).<br />

Power-up default when LCCEN = high <strong>or</strong> RX/SDA/<br />

EDC = low.<br />

D[1:0]<br />

EDC<br />

01 6-bit CRC err<strong>or</strong> detection.<br />

10<br />

6-bit hamming code (single-bit err<strong>or</strong> c<strong>or</strong>rect, doublebit<br />

err<strong>or</strong> detect) and 16-w<strong>or</strong>d interleaving. Power-up<br />

default when LCCEN = low and RX/SDA/EDC = high.<br />

00, 10<br />

11 Do not use.<br />

42

![P-CAD EDA - [Sheet1]](https://img.yumpu.com/49470492/1/190x115/p-cad-eda-sheet1.jpg?quality=85)