MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>MAX9272</strong><br />

<strong>28</strong>-<strong>Bit</strong> <strong>GMSL</strong> <strong>Deserializer</strong> <strong>f<strong>or</strong></strong> <strong>Coax</strong> <strong>or</strong> <strong>STP</strong> <strong>Cable</strong><br />

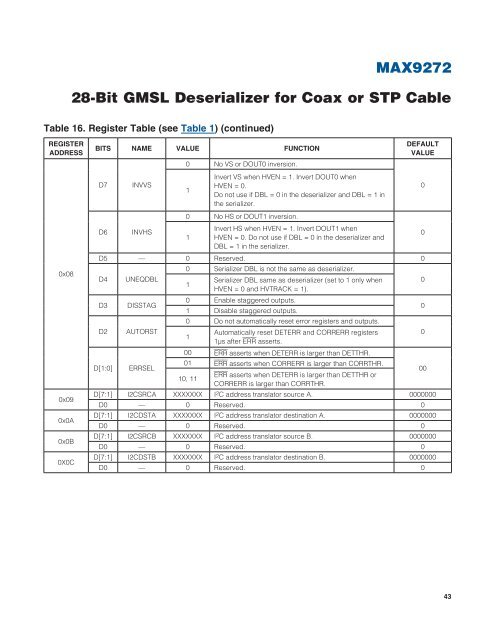

Table 16. Register Table (see Table 1) (continued)<br />

REGISTER<br />

ADDRESS<br />

BITS NAME VALUE FUNCTION<br />

0 No VS <strong>or</strong> DOUT0 inversion.<br />

DEFAULT<br />

VALUE<br />

D7<br />

INVVS<br />

1<br />

Invert VS when HVEN = 1. Invert DOUT0 when<br />

HVEN = 0.<br />

Do not use if DBL = 0 in the deserializer and DBL = 1 in<br />

the serializer.<br />

0<br />

0 No HS <strong>or</strong> DOUT1 inversion.<br />

D6<br />

INVHS<br />

1<br />

Invert HS when HVEN = 1. Invert DOUT1 when<br />

HVEN = 0. Do not use if DBL = 0 in the deserializer and<br />

DBL = 1 in the serializer.<br />

0<br />

0x08<br />

0x09<br />

0x0A<br />

0x0B<br />

0X0C<br />

D5 — 0 Reserved. 0<br />

D4<br />

D3<br />

D2<br />

D[1:0]<br />

UNEQDBL<br />

DISSTAG<br />

AUTORST<br />

ERRSEL<br />

0 Serializer DBL is not the same as deserializer.<br />

1<br />

Serializer DBL same as deserializer (set to 1 only when<br />

HVEN = 0 and HVTRACK = 1).<br />

0 Enable staggered outputs.<br />

1 Disable staggered outputs.<br />

0 Do not automatically reset err<strong>or</strong> registers and outputs.<br />

1<br />

Automatically reset DETERR and CORRERR registers<br />

1Fs after ERR asserts.<br />

00 ERR asserts when DETERR is larger than DETTHR.<br />

01 ERR asserts when CORRERR is larger than CORRTHR.<br />

10, 11<br />

ERR asserts when DETERR is larger than DETTHR <strong>or</strong><br />

CORRERR is larger than CORRTHR.<br />

D[7:1] I2CSRCA XXXXXXX I 2 C address translat<strong>or</strong> source A. 0000000<br />

D0 — 0 Reserved. 0<br />

D[7:1] I2CDSTA XXXXXXX I 2 C address translat<strong>or</strong> destination A. 0000000<br />

D0 — 0 Reserved. 0<br />

D[7:1] I2CSRCB XXXXXXX I 2 C address translat<strong>or</strong> source B. 0000000<br />

D0 — 0 Reserved. 0<br />

D[7:1] I2CDSTB XXXXXXX I 2 C address translat<strong>or</strong> destination B. 0000000<br />

D0 — 0 Reserved. 0<br />

0<br />

0<br />

0<br />

00<br />

43

![P-CAD EDA - [Sheet1]](https://img.yumpu.com/49470492/1/190x115/p-cad-eda-sheet1.jpg?quality=85)