MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

MAX9272 28-Bit GMSL Deserializer for Coax or STP Cable

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>MAX9272</strong><br />

<strong>28</strong>-<strong>Bit</strong> <strong>GMSL</strong> <strong>Deserializer</strong> <strong>f<strong>or</strong></strong> <strong>Coax</strong> <strong>or</strong> <strong>STP</strong> <strong>Cable</strong><br />

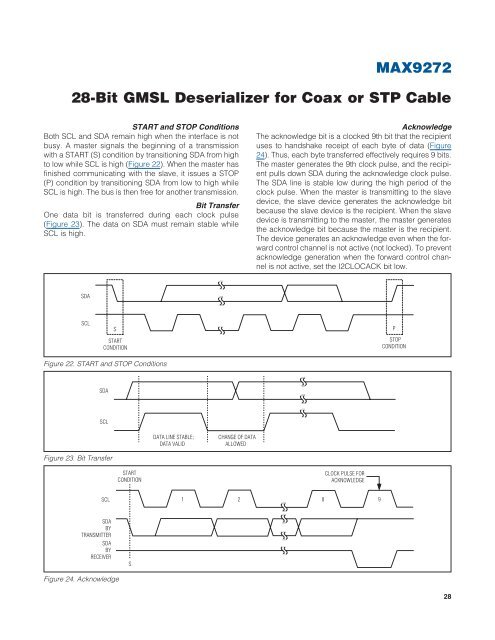

START and STOP Conditions<br />

Both SCL and SDA remain high when the interface is not<br />

busy. A master signals the beginning of a transmission<br />

with a START (S) condition by transitioning SDA from high<br />

to low while SCL is high (Figure 22). When the master has<br />

finished communicating with the slave, it issues a STOP<br />

(P) condition by transitioning SDA from low to high while<br />

SCL is high. The bus is then free <strong>f<strong>or</strong></strong> another transmission.<br />

<strong>Bit</strong> Transfer<br />

One data bit is transferred during each clock pulse<br />

(Figure 23). The data on SDA must remain stable while<br />

SCL is high.<br />

Acknowledge<br />

The acknowledge bit is a clocked 9th bit that the recipient<br />

uses to handshake receipt of each byte of data (Figure<br />

24). Thus, each byte transferred effectively requires 9 bits.<br />

The master generates the 9th clock pulse, and the recipient<br />

pulls down SDA during the acknowledge clock pulse.<br />

The SDA line is stable low during the high period of the<br />

clock pulse. When the master is transmitting to the slave<br />

device, the slave device generates the acknowledge bit<br />

because the slave device is the recipient. When the slave<br />

device is transmitting to the master, the master generates<br />

the acknowledge bit because the master is the recipient.<br />

The device generates an acknowledge even when the <strong>f<strong>or</strong></strong>ward<br />

control channel is not active (not locked). To prevent<br />

acknowledge generation when the <strong>f<strong>or</strong></strong>ward control channel<br />

is not active, set the I2CLOCACK bit low.<br />

SDA<br />

SCL<br />

S<br />

START<br />

CONDITION<br />

P<br />

STOP<br />

CONDITION<br />

Figure 22. START and STOP Conditions<br />

SDA<br />

SCL<br />

DATA LINE STABLE;<br />

DATA VALID<br />

CHANGE OF DATA<br />

ALLOWED<br />

Figure 23. <strong>Bit</strong> Transfer<br />

START<br />

CONDITION<br />

CLOCK PULSE FOR<br />

ACKNOWLEDGE<br />

SCL<br />

1 2 8 9<br />

SDA<br />

BY<br />

TRANSMITTER<br />

SDA<br />

BY<br />

RECEIVER<br />

S<br />

Figure 24. Acknowledge<br />

<strong>28</strong>

![P-CAD EDA - [Sheet1]](https://img.yumpu.com/49470492/1/190x115/p-cad-eda-sheet1.jpg?quality=85)