F224d Faria, Rubens Alexandre de Desenvolvimento de ... - UTFPR

F224d Faria, Rubens Alexandre de Desenvolvimento de ... - UTFPR

F224d Faria, Rubens Alexandre de Desenvolvimento de ... - UTFPR

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

53<br />

elementos <strong>de</strong> imagem. Urn display, por exemplo, <strong>de</strong> 320x240, possui 320 pontos na<br />

horizontal e 240 pontos na vertical. A escolha <strong>de</strong> urn display <strong>de</strong> 240x128 pontos,<br />

monocromatico, aten<strong>de</strong> as necessida<strong>de</strong>s. As caracteristicas tecnicas do display escolhido<br />

estdo <strong>de</strong>scritas no Anexo VII.<br />

4.3.4.2.1 - IMPLEMENTACAO DO LCD AO HARDWARE DA INCUBADORA<br />

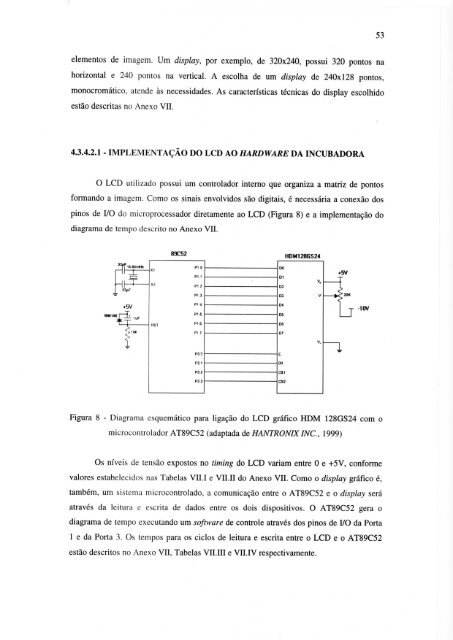

0 LCD utilizado possui urn controlador interno que organiza a matriz <strong>de</strong> pontos<br />

formando a imagem. Como os sinais envolvidos sao digitais, é necessaria a conexao dos<br />

pinos <strong>de</strong> 1/0 do microprocessador diretamente ao LCD (Figura 8) e a implementacdo do<br />

diagrama <strong>de</strong> tempo <strong>de</strong>scrito no Anexo VII.<br />

33 1 16.00 mitt<br />

pr ....<br />

1 tf_l<br />

33pF<br />

+5V<br />

DWI" —I a<br />

2IC<br />

XI<br />

I1S7<br />

89C52<br />

Pt<br />

PI.1<br />

P1 2<br />

P1.3<br />

P1 4<br />

PI.5<br />

P1 6<br />

HOM1286S24<br />

DO<br />

01<br />

+511<br />

02<br />

D3 V 20K<br />

04<br />

1 -18V<br />

Ds<br />

D6<br />

C{ 1Dk<br />

P' 7<br />

DT<br />

V<br />

P3<br />

ri I<br />

Di<br />

P3.2<br />

CSI<br />

P3 3<br />

CS7<br />

Figura 8 - Diagrama esquematico para ligacao do LCD grafico HDM 128GS24 corn o<br />

microcontrolador AT89C52 (adaptada <strong>de</strong> HANTRONIX INC., 1999)<br />

Os niveis <strong>de</strong> tensao expostos no timing do LCD variam entre 0 e +5V, conforme<br />

valores estabelecidos nas Tabelas VIII e VILII do Anexo VII. Como o display grafico é,<br />

tambem, urn sistema microcontrolado, a comunicacao entre o AT89C52 e o display sera<br />

atraves da leitura e escrita <strong>de</strong> dados entre os dois dispositivos. 0 AT89C52 gera o<br />

diagrama <strong>de</strong> tempo executando um software <strong>de</strong> controle atraves dos pinos <strong>de</strong> 1/0 da Porta<br />

1 e da Porta 3. Os tempos para os ciclos <strong>de</strong> leitura e escrita entre o LCD e o AT89C52<br />

estao <strong>de</strong>scritos no Anexo VII, Tabelas VILIII e VILIV respectivamente.