Anhang i. Simulationsmodell - FG Mikroelektronik, TU Berlin

Anhang i. Simulationsmodell - FG Mikroelektronik, TU Berlin

Anhang i. Simulationsmodell - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

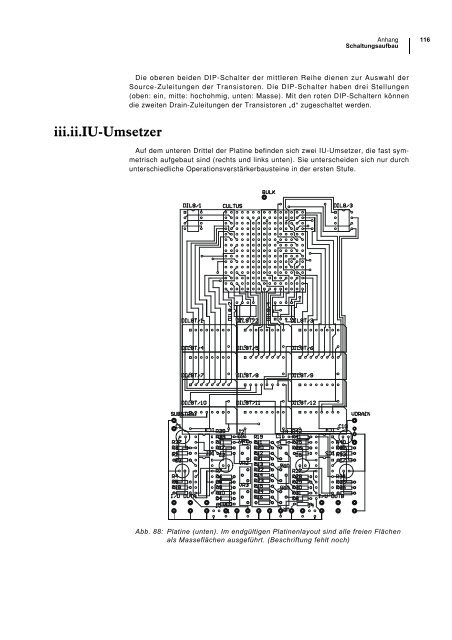

iii.ii.IU-Umsetzer<br />

<strong>Anhang</strong> 116<br />

Schaltungsaufbau<br />

Die oberen beiden DIP-Schalter der mittleren Reihe dienen zur Auswahl der<br />

Source-Zuleitungen der Transistoren. Die DIP-Schalter haben drei Stellungen<br />

(oben: ein, mitte: hochohmig, unten: Masse). Mit den roten DIP-Schaltern können<br />

die zweiten Drain-Zuleitungen der Transistoren „d“ zugeschaltet werden.<br />

Auf dem unteren Drittel der Platine befinden sich zwei IU-Umsetzer, die fast symmetrisch<br />

aufgebaut sind (rechts und links unten). Sie unterscheiden sich nur durch<br />

unterschiedliche Operationsverstärkerbausteine in der ersten Stufe.<br />

Abb. 88: Platine (unten). Im endgültigen Platinenlayout sind alle freien Flächen<br />

als Masseflächen ausgeführt. (Beschriftung fehlt noch)