Anhang i. Simulationsmodell - FG Mikroelektronik, TU Berlin

Anhang i. Simulationsmodell - FG Mikroelektronik, TU Berlin

Anhang i. Simulationsmodell - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

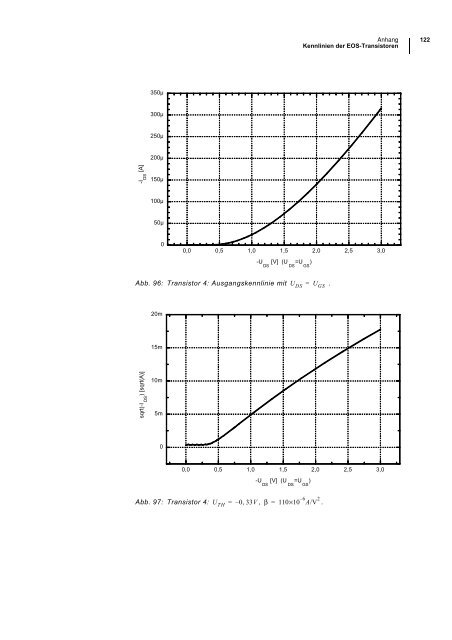

-I DS [A]<br />

350µ<br />

300µ<br />

250µ<br />

200µ<br />

150µ<br />

100µ<br />

50µ<br />

0<br />

Abb. 96: Transistor 4: Ausgangskennlinie mit = .<br />

sqrt(-I DS ) [sqrt(A)]<br />

20m<br />

15m<br />

10m<br />

5m<br />

0<br />

– 6<br />

Abb. 97: Transistor 4: = – 033V , , β 110×10<br />

A/V .<br />

2<br />

=<br />

<strong>Anhang</strong> 122<br />

Kennlinien der EOS-Transistoren<br />

0,0 0,5 1,0 1,5 2,0 2,5 3,0<br />

-U DS [V] (U DS =U GS )<br />

U DS<br />

U GS<br />

0,0 0,5 1,0 1,5 2,0 2,5 3,0<br />

U TH<br />

-U DS [V] (U DS =U GS )