4-2015

Fachzeitschrift für Elektronik-Produktion - Fertigungstechnik, Materialien und Qualitätsmanagement

Fachzeitschrift für Elektronik-Produktion - Fertigungstechnik, Materialien und Qualitätsmanagement

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Dienstleister<br />

So reduzieren Sie die Kosten<br />

für Feinleiter-Platinen<br />

Bild 3: Ausgangspreis<br />

Bild 4: Bauteilraster<br />

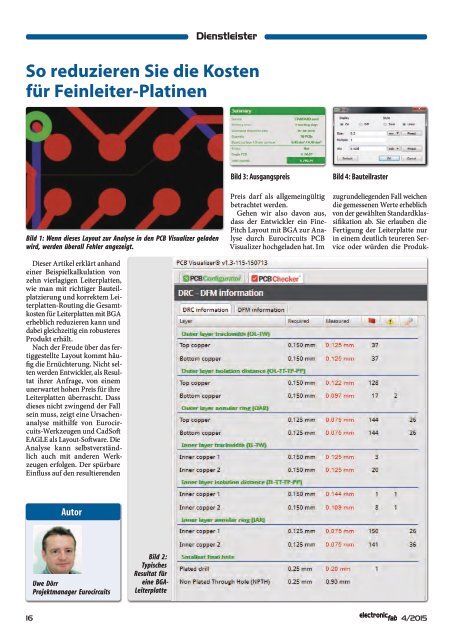

Bild 1: Wenn dieses Layout zur Analyse in den PCB Visualizer geladen<br />

wird, werden überall Fehler angezeigt.<br />

Preis darf als allgemeingültig<br />

betrachtet werden.<br />

Gehen wir also davon aus,<br />

dass der Entwickler ein Fine-<br />

Pitch Layout mit BGA zur Analyse<br />

durch Eurocircuits PCB<br />

Visualizer hochgeladen hat. Im<br />

zugrundeliegenden Fall weichen<br />

die gemessenen Werte erheblich<br />

von der gewählten Standardklassifikation<br />

ab. Sie erlauben die<br />

Fertigung der Leiterplatte nur<br />

in einem deutlich teureren Service<br />

oder würden die Produk-<br />

Dieser Artikel erklärt anhand<br />

einer Beispielkalkulation von<br />

zehn vierlagigen Leiterplatten,<br />

wie man mit richtiger Bauteilplatzierung<br />

und korrektem Leiterplatten-Routing<br />

die Gesamtkosten<br />

für Leiterplatten mit BGA<br />

erheblich reduzieren kann und<br />

dabei gleichzeitig ein robusteres<br />

Produkt erhält.<br />

Nach der Freude über das fertiggestellte<br />

Layout kommt häufig<br />

die Ernüchterung. Nicht selten<br />

werden Entwickler, als Resultat<br />

ihrer Anfrage, von einem<br />

unerwartet hohen Preis für ihre<br />

Leiterplatten überrascht. Dass<br />

dieses nicht zwingend der Fall<br />

sein muss, zeigt eine Ursachenanalyse<br />

mithilfe von Eurocircuits-Werkzeugen<br />

und CadSoft<br />

EAGLE als Layout-Software. Die<br />

Analyse kann selbstverständlich<br />

auch mit anderen Werkzeugen<br />

erfolgen. Der spürbare<br />

Einfluss auf den resultierenden<br />

Autor:<br />

Uwe Dörr<br />

Projektmanager Eurocircuits<br />

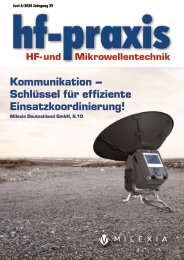

Bild 2:<br />

Typisches<br />

Resultat für<br />

eine BGA-<br />

Leiterplatte<br />

16 4/<strong>2015</strong>