ADV7174/ADV7179 Chip Scale PAL/NTSC Video ... - Analog Devices

ADV7174/ADV7179 Chip Scale PAL/NTSC Video ... - Analog Devices

ADV7174/ADV7179 Chip Scale PAL/NTSC Video ... - Analog Devices

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

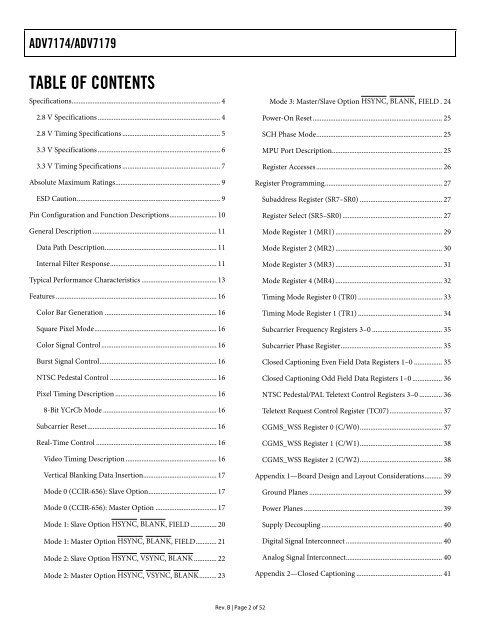

<strong>ADV7174</strong>/<strong>ADV7179</strong><br />

TABLE OF CONTENTS<br />

Specifications ..................................................................................... 4<br />

2.8 V Specifications ...................................................................... 4<br />

2.8 V Timing Specifications ........................................................ 5<br />

3.3 V Specifications ...................................................................... 6<br />

3.3 V Timing Specifications ........................................................ 7<br />

Absolute Maximum Ratings ............................................................ 9<br />

ESD Caution .................................................................................. 9<br />

Pin Configuration and Function Descriptions ........................... 10<br />

General Description ....................................................................... 11<br />

Data Path Description ................................................................ 11<br />

Internal Filter Response ............................................................. 11<br />

Typical Performance Characteristics ........................................... 13<br />

Features ............................................................................................ 16<br />

Color Bar Generation ................................................................ 16<br />

Square Pixel Mode ...................................................................... 16<br />

Color Signal Control .................................................................. 16<br />

Burst Signal Control ................................................................... 16<br />

<strong>NTSC</strong> Pedestal Control ............................................................. 16<br />

Pixel Timing Description .......................................................... 16<br />

8-Bit YCrCb Mode ................................................................. 16<br />

Subcarrier Reset .......................................................................... 16<br />

Real-Time Control ..................................................................... 16<br />

<strong>Video</strong> Timing Description .................................................... 16<br />

Vertical Blanking Data Insertion.......................................... 17<br />

Mode 0 (CCIR-656): Slave Option ....................................... 17<br />

Mode 0 (CCIR-656): Master Option ................................... 17<br />

Mode 1: Slave Option HSYNC, BLANK, FIELD ............... 20<br />

Mode 1: Master Option HSYNC, BLANK, FIELD ............ 21<br />

Mode 2: Slave Option HSYNC, VSYNC, BLANK ............. 22<br />

Mode 2: Master Option HSYNC, VSYNC, BLANK .......... 23<br />

Rev. B | Page 2 of 52<br />

Mode 3: Master/Slave Option HSYNC, BLANK, FIELD . 24<br />

Power-On Reset .......................................................................... 25<br />

SCH Phase Mode ........................................................................ 25<br />

MPU Port Description ............................................................... 25<br />

Register Accesses ........................................................................ 26<br />

Register Programming ................................................................... 27<br />

Subaddress Register (SR7–SR0) ............................................... 27<br />

Register Select (SR5–SR0) ......................................................... 27<br />

Mode Register 1 (MR1) ............................................................. 29<br />

Mode Register 2 (MR2) ............................................................. 30<br />

Mode Register 3 (MR3) ............................................................. 31<br />

Mode Register 4 (MR4) ............................................................. 32<br />

Timing Mode Register 0 (TR0) ................................................ 33<br />

Timing Mode Register 1 (TR1) ................................................ 34<br />

Subcarrier Frequency Registers 3–0 ........................................ 35<br />

Subcarrier Phase Register .......................................................... 35<br />

Closed Captioning Even Field Data Registers 1–0 ................ 35<br />

Closed Captioning Odd Field Data Registers 1–0 ................. 36<br />

<strong>NTSC</strong> Pedestal/<strong>PAL</strong> Teletext Control Registers 3–0 ............. 36<br />

Teletext Request Control Register (TC07) .............................. 37<br />

CGMS_WSS Register 0 (C/W0) ............................................... 37<br />

CGMS_WSS Register 1 (C/W1) ............................................... 38<br />

CGMS_WSS Register 2 (C/W2) ............................................... 38<br />

Appendix 1—Board Design and Layout Considerations .......... 39<br />

Ground Planes ............................................................................ 39<br />

Power Planes ............................................................................... 39<br />

Supply Decoupling ..................................................................... 40<br />

Digital Signal Interconnect ....................................................... 40<br />

<strong>Analog</strong> Signal Interconnect....................................................... 40<br />

Appendix 2—Closed Captioning ................................................. 41