ADV7174/ADV7179 Chip Scale PAL/NTSC Video ... - Analog Devices

ADV7174/ADV7179 Chip Scale PAL/NTSC Video ... - Analog Devices

ADV7174/ADV7179 Chip Scale PAL/NTSC Video ... - Analog Devices

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

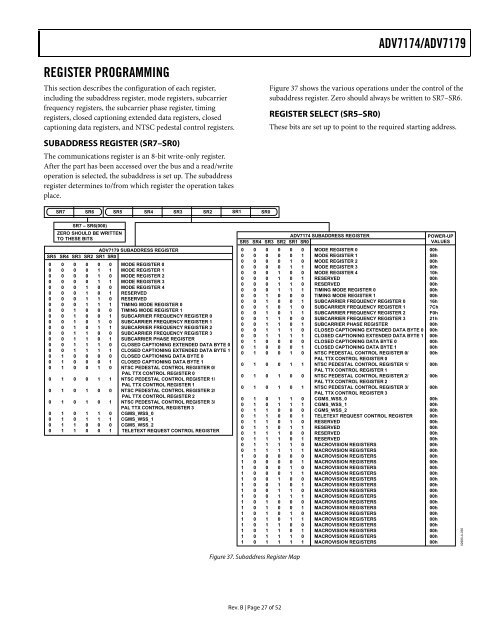

REGISTER PROGRAMMING<br />

This section describes the configuration of each register,<br />

including the subaddress register, mode registers, subcarrier<br />

frequency registers, the subcarrier phase register, timing<br />

registers, closed captioning extended data registers, closed<br />

captioning data registers, and <strong>NTSC</strong> pedestal control registers.<br />

SUBADDRESS REGISTER (SR7–SR0)<br />

The communications register is an 8-bit write-only register.<br />

After the part has been accessed over the bus and a read/write<br />

operation is selected, the subaddress is set up. The subaddress<br />

register determines to/from which register the operation takes<br />

place.<br />

SR7 SR6 SR5<br />

SR7 – SR6(000)<br />

ZERO SHOULD BE WRITTEN<br />

TO THESE BITS<br />

SR4 SR3 SR2 SR1 SR0<br />

SR5<br />

<strong>ADV7179</strong> SUBADDRESS REGISTER<br />

SR4 SR3 SR2 SR1 SR0<br />

0 0 0 0 0 0 MODE REGISTER 0<br />

0 0 0 0 1 1 MODE REGISTER 1<br />

0 0 0 0 1 0 MODE REGISTER 2<br />

0 0 0 0 1 1 MODE REGISTER 3<br />

0 0 0 1 0 0 MODE REGISTER 4<br />

0 0 0 1 0 1 RESERVED<br />

0 0 0 1 1 0 RESERVED<br />

0 0 0 1 1 1 TIMING MODE REGISTER 0<br />

0 0 1 0 0 0 TIMING MODE REGISTER 1<br />

0 0 1 0 0 1 SUBCARRIER FREQUENCY REGISTER 0<br />

0 0 1 0 1 0 SUBCARRIER FREQUENCY REGISTER 1<br />

0 0 1 0 1 1 SUBCARRIER FREQUENCY REGISTER 2<br />

0 0 1 1 0 0 SUBCARRIER FREQUENCY REGISTER 3<br />

0 0 1 1 0 1 SUBCARRIER PHASE REGISTER<br />

0 0 1 1 1 0 CLOSED CAPTIONING EXTENDED DATA BYTE 0<br />

0 0 1 1 1 1 CLOSED CAPTIONING EXTENDED DATA BYTE 1<br />

0 1 0 0 0 0 CLOSED CAPTIONING DATA BYTE 0<br />

0 1 0 0 0 1 CLOSED CAPTIONING DATA BYTE 1<br />

0 1 0 0 1 0 <strong>NTSC</strong> PEDESTAL CONTROL REGISTER 0/<br />

<strong>PAL</strong> TTX CONTROL REGISTER 0<br />

0 1 0 0 1 1 <strong>NTSC</strong> PEDESTAL CONTROL REGISTER 1/<br />

<strong>PAL</strong> TTX CONTROL REGISTER 1<br />

0 1 0 1 0 0 <strong>NTSC</strong> PEDESTAL CONTROL REGISTER 2/<br />

<strong>PAL</strong> TTX CONTROL REGISTER 2<br />

0 1 0 1 0 1 <strong>NTSC</strong> PEDESTAL CONTROL REGISTER 3/<br />

<strong>PAL</strong> TTX CONTROL REGISTER 3<br />

0 1 0 1 1 0 CGMS_WSS_0<br />

0 1 0 1 1 1 CGMS_WSS_1<br />

0 1 1 0 0 0 CGMS_WSS_2<br />

0 1 1 0 0 1 TELETEXT REQUEST CONTROL REGISTER<br />

Rev. B | Page 27 of 52<br />

<strong>ADV7174</strong>/<strong>ADV7179</strong><br />

Figure 37 shows the various operations under the control of the<br />

subaddress register. Zero should always be written to SR7–SR6.<br />

REGISTER SELECT (SR5–SR0)<br />

These bits are set up to point to the required starting address.<br />

SR5<br />

<strong>ADV7174</strong> SUBADDRESS REGISTER<br />

SR4 SR3 SR2 SR1 SR0<br />

0 0 0 0 0 0 MODE REGISTER 0<br />

0 0 0 0 0 1 MODE REGISTER 1<br />

0 0 0 0 1 0 MODE REGISTER 2<br />

0 0 0 0 1 1 MODE REGISTER 3<br />

0 0 0 1 0 0 MODE REGISTER 4<br />

0 0 0 1 0 1 RESERVED<br />

0 0 0 1 1 0 RESERVED<br />

0 0 0 1 1 1 TIMING MODE REGISTER 0<br />

0 0 1 0 0 0 TIMING MODE REGISTER 1<br />

0 0 1 0 0 1 SUBCARRIER FREQUENCY REGISTER 0<br />

0 0 1 0 1 0 SUBCARRIER FREQUENCY REGISTER 1<br />

0 0 1 0 1 1 SUBCARRIER FREQUENCY REGISTER 2<br />

0 0 1 1 0 0 SUBCARRIER FREQUENCY REGISTER 3<br />

0 0 1 1 0 1 SUBCARRIER PHASE REGISTER<br />

0 0 1 1 1 0 CLOSED CAPTIONING EXTENDED DATA BYTE 0<br />

0 0 1 1 1 1 CLOSED CAPTIONING EXTENDED DATA BYTE 1<br />

0 1 0 0 0 0 CLOSED CAPTIONING DATA BYTE 0<br />

0 1 0 0 0 1 CLOSED CAPTIONING DATA BYTE 1<br />

0 1 0 0 1 0 <strong>NTSC</strong> PEDESTAL CONTROL REGISTER 0/<br />

<strong>PAL</strong> TTX CONTROL REGISTER 0<br />

0 1 0 0 1 1 <strong>NTSC</strong> PEDESTAL CONTROL REGISTER 1/<br />

<strong>PAL</strong> TTX CONTROL REGISTER 1<br />

0 1 0 1 0 0 <strong>NTSC</strong> PEDESTAL CONTROL REGISTER 2/<br />

<strong>PAL</strong> TTX CONTROL REGISTER 2<br />

0 1 0 1 0 1 <strong>NTSC</strong> PEDESTAL CONTROL REGISTER 3/<br />

<strong>PAL</strong> TTX CONTROL REGISTER 3<br />

0 1 0 1 1 0 CGMS_WSS_0<br />

0 1 0 1 1 1 CGMS_WSS_1<br />

0 1 1 0 0 0 CGMS_WSS_2<br />

0 1 1 0 0 1 TELETEXT REQUEST CONTROL REGISTER<br />

0 1 1 0 1 0 RESERVED<br />

0 1 1 0 1 1 RESERVED<br />

0 1 1 1 0 0 RESERVED<br />

0 1 1 1 0 1 RESERVED<br />

0 1 1 1 1 0 MACROVISION REGISTERS<br />

0 1 1 1 1 1 MACROVISION REGISTERS<br />

1 0 0 0 0 0 MACROVISION REGISTERS<br />

1 0 0 0 0 1 MACROVISION REGISTERS<br />

1 0 0 0 1 0 MACROVISION REGISTERS<br />

1 0 0 0 1 1 MACROVISION REGISTERS<br />

1 0 0 1 0 0 MACROVISION REGISTERS<br />

1 0 0 1 0 1 MACROVISION REGISTERS<br />

1 0 0 1 1 0 MACROVISION REGISTERS<br />

1 0 0 1 1 1 MACROVISION REGISTERS<br />

1 0 1 0 0 0 MACROVISION REGISTERS<br />

1 0 1 0 0 1 MACROVISION REGISTERS<br />

1 0 1 0 1 0 MACROVISION REGISTERS<br />

1 0 1 0 1 1 MACROVISION REGISTERS<br />

1 0 1 1 0 0 MACROVISION REGISTERS<br />

1 0 1 1 0 1 MACROVISION REGISTERS<br />

1 0 1 1 1 0 MACROVISION REGISTERS<br />

1 0 1 1 1 1 MACROVISION REGISTERS<br />

Figure 37. Subaddress Register Map<br />

POWER-UP<br />

VALUES<br />

00h<br />

58h<br />

00h<br />

00h<br />

10h<br />

00h<br />

00h<br />

00h<br />

00h<br />

16h<br />

7Ch<br />

F0h<br />

21h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

00h<br />

02980-A-036