Synchrophasor Initiative in India - erldc

Synchrophasor Initiative in India - erldc

Synchrophasor Initiative in India - erldc

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

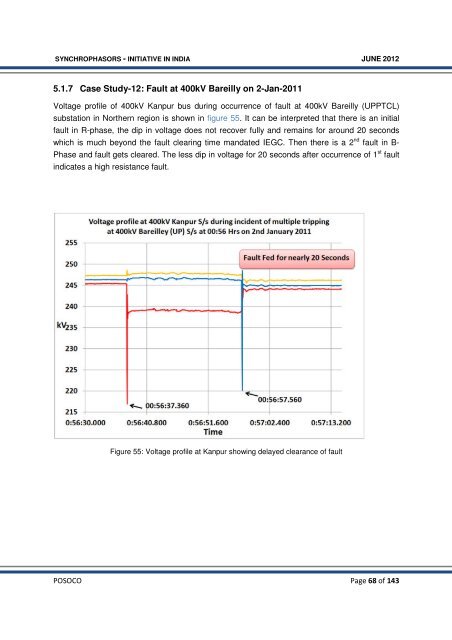

SYNCHROPHASORS - INITIATIVE IN INDIA JUNE 20125.1.7 Case Study-12: Fault at 400kV Bareilly on 2-Jan-2011Voltage profile of 400kV Kanpur bus dur<strong>in</strong>g occurrence of fault at 400kV Bareilly (UPPTCL)substation <strong>in</strong> Northern region is shown <strong>in</strong> figure 55. It can be <strong>in</strong>terpreted that there is an <strong>in</strong>itialfault <strong>in</strong> R-phase, the dip <strong>in</strong> voltage does not recover fully and rema<strong>in</strong>s for around 20 secondswhich is much beyond the fault clear<strong>in</strong>g time mandated IEGC. Then there is a 2 nd fault <strong>in</strong> B-Phase and fault gets cleared. The less dip <strong>in</strong> voltage for 20 seconds after occurrence of 1 st fault<strong>in</strong>dicates a high resistance fault.Figure 55: Voltage profile at Kanpur show<strong>in</strong>g delayed clearance of faultPOSOCO Page 68 of 143