PDF version - ARM Information Center

PDF version - ARM Information Center

PDF version - ARM Information Center

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

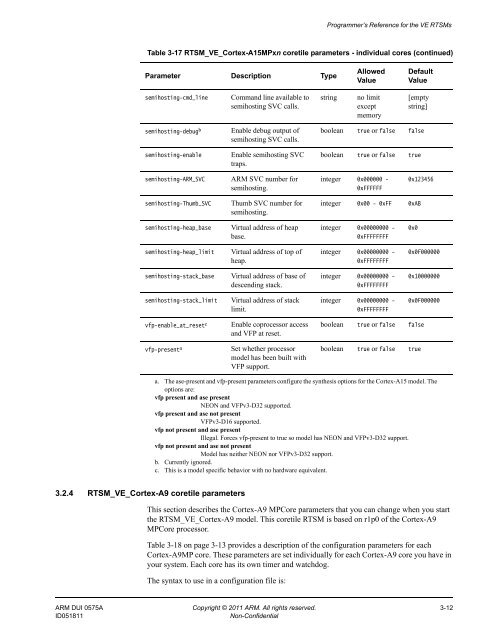

Programmer’s Reference for the VE RTSMsTable 3-17 RTSM_VE_Cortex-A15MPxn coretile parameters - individual cores (continued)Parameter Description TypeAllowedValueDefaultValuesemihosting-cmd_lineCommand line available tosemihosting SVC calls.stringno limitexceptmemory[emptystring]semihosting-debug bsemihosting-enableEnable debug output ofsemihosting SVC calls.Enable semihosting SVCtraps.boolean true or false falseboolean true or false truesemihosting-<strong>ARM</strong>_SVC<strong>ARM</strong> SVC number forsemihosting.integer 0x000000 -0xFFFFFF0x123456semihosting-Thumb_SVCThumb SVC number forsemihosting.integer 0x00 - 0xFF 0xABsemihosting-heap_baseVirtual address of heapbase.integer 0x00000000 -0xFFFFFFFF0x0semihosting-heap_limitVirtual address of top ofheap.integer 0x00000000 -0xFFFFFFFF0x0F000000semihosting-stack_baseVirtual address of base ofdescending stack.integer 0x00000000 -0xFFFFFFFF0x10000000semihosting-stack_limitVirtual address of stacklimit.integer 0x00000000 -0xFFFFFFFF0x0F000000vfp-enable_at_reset cvfp-present aEnable coprocessor accessand VFP at reset.Set whether processormodel has been built withVFP support.boolean true or false falseboolean true or false truea. The ase-present and vfp-present parameters configure the synthesis options for the Cortex-A15 model. Theoptions are:vfp present and ase presentNEON and VFPv3-D32 supported.vfp present and ase not presentVFPv3-D16 supported.vfp not present and ase presentIllegal. Forces vfp-present to true so model has NEON and VFPv3-D32 support.vfp not present and ase not presentModel has neither NEON nor VFPv3-D32 support.b. Currently ignored.c. This is a model specific behavior with no hardware equivalent.3.2.4 RTSM_VE_Cortex-A9 coretile parametersThis section describes the Cortex-A9 MPCore parameters that you can change when you startthe RTSM_VE_Cortex-A9 model. This coretile RTSM is based on r1p0 of the Cortex-A9MPCore processor.Table 3-18 on page 3-13 provides a description of the configuration parameters for eachCortex-A9MP core. These parameters are set individually for each Cortex-A9 core you have inyour system. Each core has its own timer and watchdog.The syntax to use in a configuration file is:<strong>ARM</strong> DUI 0575A Copyright © 2011 <strong>ARM</strong>. All rights reserved. 3-12ID051811Non-Confidential