PDF version - ARM Information Center

PDF version - ARM Information Center

PDF version - ARM Information Center

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

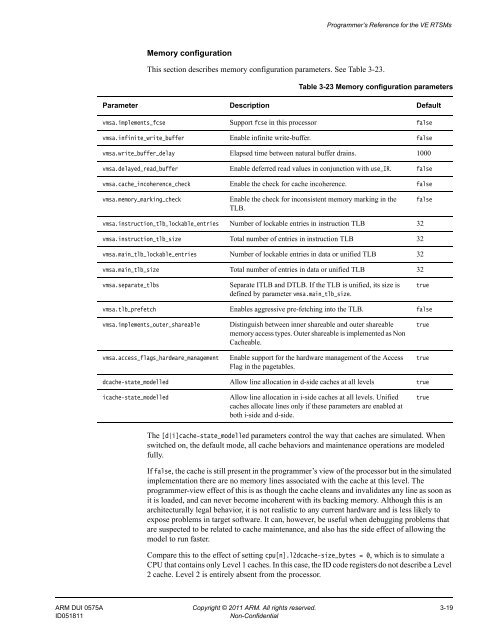

Programmer’s Reference for the VE RTSMsMemory configurationThis section describes memory configuration parameters. See Table 3-23.Table 3-23 Memory configuration parametersParameter Description Defaultvmsa.implements_fcse Support fcse in this processor falsevmsa.infinite_write_buffer Enable infinite write-buffer. falsevmsa.write_buffer_delay Elapsed time between natural buffer drains. 1000vmsa.delayed_read_buffer Enable deferred read values in conjunction with use_IR. falsevmsa.cache_incoherence_check Enable the check for cache incoherence. falsevmsa.memory_marking_checkEnable the check for inconsistent memory marking in theTLB.falsevmsa.instruction_tlb_lockable_entries Number of lockable entries in instruction TLB 32vmsa.instruction_tlb_size Total number of entries in instruction TLB 32vmsa.main_tlb_lockable_entries Number of lockable entries in data or unified TLB 32vmsa.main_tlb_size Total number of entries in data or unified TLB 32vmsa.separate_tlbsSeparate ITLB and DTLB. If the TLB is unified, its size isdefined by parameter vmsa.main_tlb_size.truevmsa.tlb_prefetch Enables aggressive pre-fetching into the TLB. falsevmsa.implements_outer_shareablevmsa.access_flags_hardware_managementDistinguish between inner shareable and outer shareablememory access types. Outer shareable is implemented as NonCacheable.Enable support for the hardware management of the AccessFlag in the pagetables.truetruedcache-state_modelled Allow line allocation in d-side caches at all levels trueicache-state_modelledAllow line allocation in i-side caches at all levels. Unifiedcaches allocate lines only if these parameters are enabled atboth i-side and d-side.trueThe [d|i]cache-state_modelled parameters control the way that caches are simulated. Whenswitched on, the default mode, all cache behaviors and maintenance operations are modeledfully.If false, the cache is still present in the programmer’s view of the processor but in the simulatedimplementation there are no memory lines associated with the cache at this level. Theprogrammer-view effect of this is as though the cache cleans and invalidates any line as soon asit is loaded, and can never become incoherent with its backing memory. Although this is anarchitecturally legal behavior, it is not realistic to any current hardware and is less likely toexpose problems in target software. It can, however, be useful when debugging problems thatare suspected to be related to cache maintenance, and also has the side effect of allowing themodel to run faster.Compare this to the effect of setting cpu[n].l2dcache-size_bytes = 0, which is to simulate aCPU that contains only Level 1 caches. In this case, the ID code registers do not describe a Level2 cache. Level 2 is entirely absent from the processor.<strong>ARM</strong> DUI 0575A Copyright © 2011 <strong>ARM</strong>. All rights reserved. 3-19ID051811Non-Confidential