PDF version - ARM Information Center

PDF version - ARM Information Center

PDF version - ARM Information Center

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

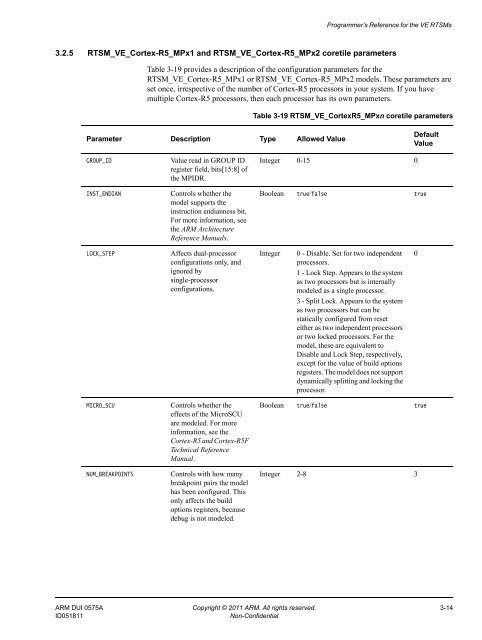

Programmer’s Reference for the VE RTSMs3.2.5 RTSM_VE_Cortex-R5_MPx1 and RTSM_VE_Cortex-R5_MPx2 coretile parametersTable 3-19 provides a description of the configuration parameters for theRTSM_VE_Cortex-R5_MPx1 or RTSM_VE_Cortex-R5_MPx2 models. These parameters areset once, irrespective of the number of Cortex-R5 processors in your system. If you havemultiple Cortex-R5 processors, then each processor has its own parameters.Table 3-19 RTSM_VE_CortexR5_MPxn coretile parametersParameter Description Type Allowed ValueDefaultValueGROUP_IDINST_ENDIANValue read in GROUP IDregister field, bits[15:8] ofthe MPIDR.Controls whether themodel supports theinstruction endianness bit.For more information, seethe <strong>ARM</strong> ArchitectureReference Manuals.Integer 0-15 0Boolean true/false trueLOCK_STEPAffects dual-processorconfigurations only, andignored bysingle-processorconfigurations.Integer0 - Disable. Set for two independentprocessors.1 - Lock Step. Appears to the systemas two processors but is internallymodeled as a single processor.3 - Split Lock. Appears to the systemas two processors but can bestatically configured from reseteither as two independent processorsor two locked processors. For themodel, these are equivalent toDisable and Lock Step, respectively,except for the value of build optionsregisters. The model does not supportdynamically splitting and locking theprocessor.0MICRO_SCUNUM_BREAKPOINTSControls whether theeffects of the MicroSCUare modeled. For moreinformation, see theCortex-R5 and Cortex-R5FTechnical ReferenceManual.Controls with how manybreakpoint pairs the modelhas been configured. Thisonly affects the buildoptions registers, becausedebug is not modeled.Boolean true/false trueInteger 2-8 3<strong>ARM</strong> DUI 0575A Copyright © 2011 <strong>ARM</strong>. All rights reserved. 3-14ID051811Non-Confidential