- Page 1 and 2: A 1.5-V 900-Mhz Monolithic CMOSFast

- Page 3 and 4: A 1.5-V 900-Mhz Monolithic CMOS Fas

- Page 5 and 6: Table of ContentsPageAcknowledgment

- Page 7 and 8: Testing setup......................

- Page 9 and 10: List of FiguresPageFig. 1 Block dia

- Page 11 and 12: Fig. 76 Amplitudes and currents of

- Page 13 and 14: Chapter 1 IntroductionBackgroundWir

- Page 15 and 16: applications because it can provide

- Page 17 and 18: existing monolithic frequency synth

- Page 19 and 20: the receiver frequency band is from

- Page 21 and 22: out-of-bandin-bandout-of-band0dBmin

- Page 23 and 24: Based on the maximum interference,

- Page 25 and 26: carrierdBcspur∆fFig. 8 Frequency

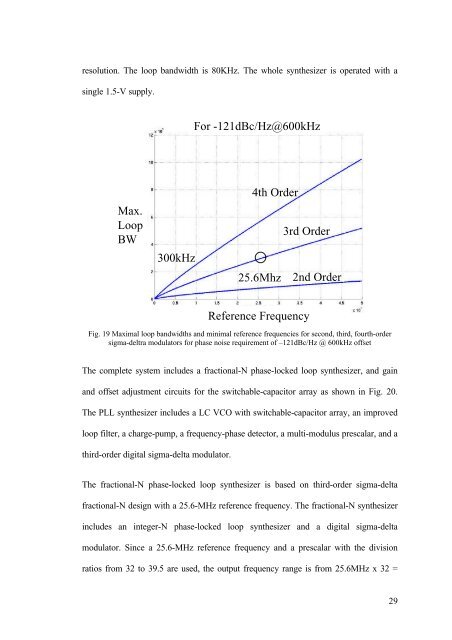

- Page 27 and 28: Spurs requirement (dBc)Frequency of

- Page 29 and 30: The frequency diversity can be perf

- Page 31 and 32: Chapter 3 System DesignPhase-locked

- Page 33 and 34: coarse tuning can be provided by th

- Page 35 and 36: array is now possible. Moreover, th

- Page 37 and 38: performance of the synthesizer 9 .

- Page 39: signalquantizationnoisea) f b)signa

- Page 43 and 44: the output value between 0 and 0.5,

- Page 45 and 46: The coupled-LC oscillators can be v

- Page 47 and 48: 890MHzf25MHz243KHz865MHzFig. 23 Tun

- Page 49 and 50: onoffCwellClinearCwellClinearCwellC

- Page 51 and 52: spirals of similar sizes is around

- Page 53 and 54: in Fig. 27a and Fig. 27b, the same

- Page 55 and 56: conductance (Gm) and the reciprocal

- Page 57 and 58: −19⎛ 900M⎞0.0259×1.6×10 ×

- Page 59 and 60: GdoVinFig. 32 Gdo of the proposed L

- Page 61 and 62: RzCzIcpCpR4C4a)IcpCzR4B.IcpCpRpC4b)

- Page 63 and 64: Usually, capacitors in the filter o

- Page 65 and 66: RVinFig. 38 Resistance of NMOS resi

- Page 67 and 68: feedback path to prevent the proble

- Page 69 and 70: 890MHz25MHz865MHzfA+∆A

- Page 71 and 72: High-speed multi-modulus dividerThe

- Page 73 and 74: CLKQBQDDBFig. 50 Schematic diagram

- Page 75 and 76: ANDgateABclkclkclkclkQBFig. 54 Sche

- Page 77 and 78: f o/2 /2,3 /2,3 /2 /2f div/4Combina

- Page 79 and 80: next stage, as shown in the Fig. 59

- Page 81 and 82: co10bDclkclkFig. 60 Schematic of th

- Page 83 and 84: (1-Z -1 ) 23bDQBclkZ -1 (1-Z -1 )2b

- Page 85 and 86: X 16clkDclkQBDclkQBFig. 66 Schemati

- Page 87 and 88: ~90 oa) b) c)Fig. 68 Different meth

- Page 89 and 90: (dotted line). As the oscillation c

- Page 91 and 92:

In practice, it is not desirable to

- Page 93 and 94:

and decrease in amplitude mismatch

- Page 95 and 96:

Current interactionThe two oscillat

- Page 97 and 98:

equirements. Fortunately, by connec

- Page 99 and 100:

LC oscillators are put apart to red

- Page 101 and 102:

Gain mismatch (in %)Two oscillators

- Page 103 and 104:

equals to1 . By doubling the height

- Page 105 and 106:

30 is obtained. It is because the s

- Page 107 and 108:

The spiral inductor is designed and

- Page 109 and 110:

oscillators (shown in the upper and

- Page 111 and 112:

Synthesizer LayoutThe layout and th

- Page 113 and 114:

Die LayoutFig. 98 shows the die pho

- Page 115 and 116:

Testing setupThe testing setup show

- Page 117 and 118:

Resistance (ohms)Freq (Hz)Fig. 101

- Page 119 and 120:

Resistance (ohms)Freq (Hz)Fig. 105

- Page 121 and 122:

VaractorFig. 109 shows the testing

- Page 123 and 124:

Table 5 Summary of parameters of va

- Page 125 and 126:

Table 6 Summary of N-well substrate

- Page 127 and 128:

Fig. 120 Quality factor of the swit

- Page 129 and 130:

The decrease in quality factor is d

- Page 131 and 132:

Fig. 126 Schematic diagram of the p

- Page 133 and 134:

Output frequency(MHz)Number of swit

- Page 135 and 136:

Gain (MHz/V)Tuning voltage (v)Fig.

- Page 137 and 138:

on the process variation. Therefore

- Page 139 and 140:

voltage (Vos = Rp x Ios) appeared.

- Page 141 and 142:

Although the spurs are quite large,

- Page 143 and 144:

GMSK signals with 0.3 BT and a bit

- Page 145 and 146:

Power spectral density (dB)(b)(a)(c

- Page 147 and 148:

Summary of performanceA summary of

- Page 149 and 150:

Table 10 Comparison of performances

- Page 151 and 152:

As the voltage-controlled oscillato

- Page 153 and 154:

Bibliography1 Thomas H. Lee, The De