MPhil thesis of Lo Chi Wa - Department of Electronic & Computer ...

MPhil thesis of Lo Chi Wa - Department of Electronic & Computer ...

MPhil thesis of Lo Chi Wa - Department of Electronic & Computer ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

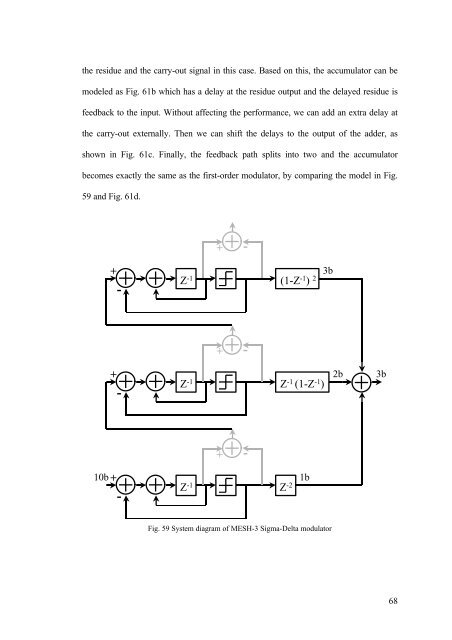

the residue and the carry-out signal in this case. Based on this, the accumulator can bemodeled as Fig. 61b which has a delay at the residue output and the delayed residue isfeedback to the input. Without affecting the performance, we can add an extra delay atthe carry-out externally. Then we can shift the delays to the output <strong>of</strong> the adder, asshown in Fig. 61c. Finally, the feedback path splits into two and the accumulatorbecomes exactly the same as the first-order modulator, by comparing the model in Fig.59 and Fig. 61d.+-Z -1 + -(1-Z -1 ) 23b+-Z -1 + -Z -1 (1-Z -1 )2b3b10b +-Z -1 + -Z -21bFig. 59 System diagram <strong>of</strong> MESH-3 Sigma-Delta modulator68