MPhil thesis of Lo Chi Wa - Department of Electronic & Computer ...

MPhil thesis of Lo Chi Wa - Department of Electronic & Computer ...

MPhil thesis of Lo Chi Wa - Department of Electronic & Computer ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

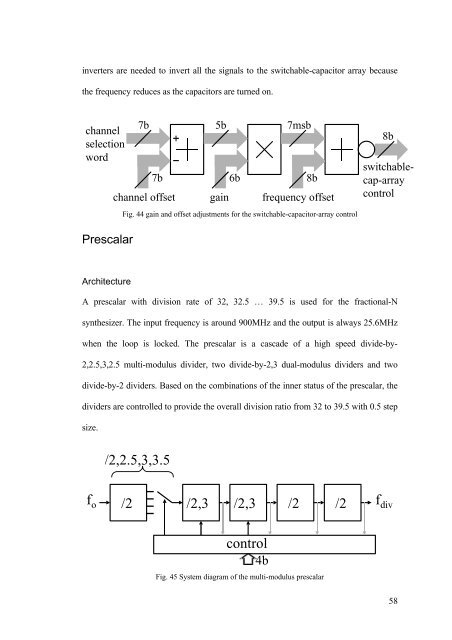

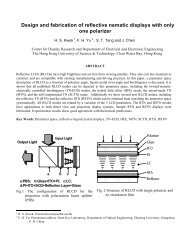

inverters are needed to invert all the signals to the switchable-capacitor array becausethe frequency reduces as the capacitors are turned on.channelselectionword7b7b5b6b7msbchannel <strong>of</strong>fset gain frequency <strong>of</strong>fsetFig. 44 gain and <strong>of</strong>fset adjustments for the switchable-capacitor-array control8b8bswitchablecap-arraycontrolPrescalarArchitectureA prescalar with division rate <strong>of</strong> 32, 32.5 … 39.5 is used for the fractional-Nsynthesizer. The input frequency is around 900MHz and the output is always 25.6MHzwhen the loop is locked. The prescalar is a cascade <strong>of</strong> a high speed divide-by-2,2.5,3,2.5 multi-modulus divider, two divide-by-2,3 dual-modulus dividers and twodivide-by-2 dividers. Based on the combinations <strong>of</strong> the inner status <strong>of</strong> the prescalar, thedividers are controlled to provide the overall division ratio from 32 to 39.5 with 0.5 stepsize./2,2.5,3,3.5f o/2 /2,3 /2,3 /2 /2f divcontrol4bFig. 45 System diagram <strong>of</strong> the multi-modulus prescalar58