pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

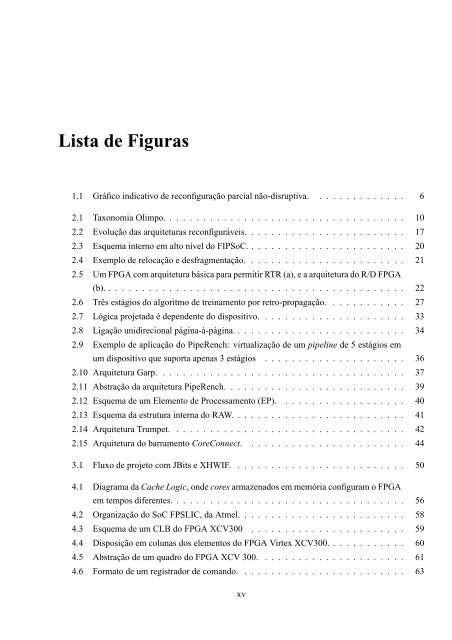

Lista <strong>de</strong> Figuras<br />

1.1 Gráfico indicativo <strong>de</strong> reconfiguração parcial não-disruptiva. . . . . . . . . . . . . . 6<br />

2.1 Taxonomia Olimpo. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10<br />

2.2 Evolução das arquiteturas reconfiguráveis. . . . . . . . . . . . . . . . . . . . . . . . 17<br />

2.3 Esquema interno em alto nível do FIPSoC. . . . . . . . . . . . . . . . . . . . . . . . 20<br />

2.4 Exemplo <strong>de</strong> relocação e <strong>de</strong>sfragmentação. . . . . . . . . . . . . . . . . . . . . . . . 21<br />

2.5 Um FPGA com arquitetura básica para permitir RTR (a), e a arquitetura do R/D FPGA<br />

(b). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22<br />

2.6 Três estágios do algoritmo <strong>de</strong> treinamento por retro-propagação. . . . . . . . . . . . 27<br />

2.7 Lógica projetada é <strong>de</strong>pen<strong>de</strong>nte do dispositivo. . . . . . . . . . . . . . . . . . . . . . 33<br />

2.8 Ligação unidirecional página-à-página. . . . . . . . . . . . . . . . . . . . . . . . . . 34<br />

2.9 Exemplo <strong>de</strong> aplicação do PipeRench: virtualização <strong>de</strong> um pipeline <strong>de</strong> 5 estágios em<br />

um dispositivo que suporta apenas 3 estágios . . . . . . . . . . . . . . . . . . . . . 36<br />

2.10 Arquitetura Garp. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37<br />

2.11 Abstração da arquitetura PipeRench. . . . . . . . . . . . . . . . . . . . . . . . . . . 39<br />

2.12 Esquema <strong>de</strong> um Elemento <strong>de</strong> Processamento (EP). . . . . . . . . . . . . . . . . . . 40<br />

2.13 Esquema da estrutura interna do RAW. . . . . . . . . . . . . . . . . . . . . . . . . . 41<br />

2.14 Arquitetura Trumpet. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42<br />

2.15 Arquitetura do barramento CoreConnect. . . . . . . . . . . . . . . . . . . . . . . . 44<br />

3.1 Fluxo <strong>de</strong> projeto com JBits e XHWIF. . . . . . . . . . . . . . . . . . . . . . . . . . 50<br />

4.1 Diagrama da Cache Logic, on<strong>de</strong> cores armazenados em memória configuram o FPGA<br />

em tempos diferentes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56<br />

4.2 Organização do SoC FPSLIC, da Atmel. . . . . . . . . . . . . . . . . . . . . . . . . 58<br />

4.3 Esquema <strong>de</strong> um CLB do FPGA XCV300 . . . . . . . . . . . . . . . . . . . . . . . 59<br />

4.4 Disposição em colunas dos elementos do FPGA Virtex XCV300. . . . . . . . . . . . 60<br />

4.5 Abstração <strong>de</strong> um quadro do FPGA XCV 300. . . . . . . . . . . . . . . . . . . . . . 61<br />

4.6 Formato <strong>de</strong> um registrador <strong>de</strong> comando. . . . . . . . . . . . . . . . . . . . . . . . . 63<br />

xv