pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

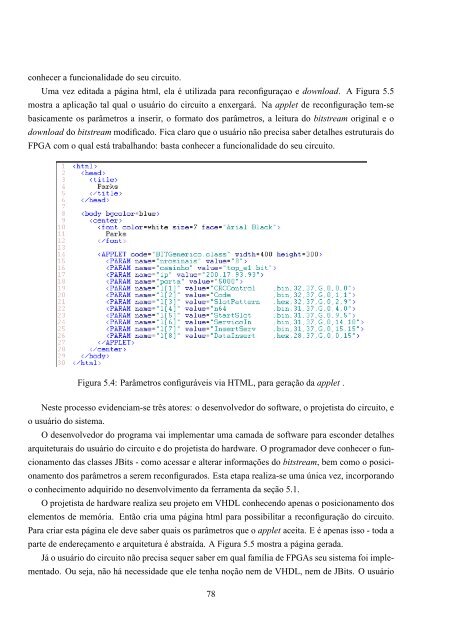

conhecer a funcionalida<strong>de</strong> do seu circuito.<br />

Uma vez editada a página html, ela é utilizada para reconfiguraçao e download. A Figura 5.5<br />

mostra a aplicação tal qual o usuário do circuito a enxergará. Na applet <strong>de</strong> reconfiguração tem-se<br />

basicamente os parâmetros a inserir, o formato dos parâmetros, a leitura do bitstream original e o<br />

download do bitstream modificado. Fica claro que o usuário não precisa saber <strong>de</strong>talhes estruturais do<br />

FPGA com o qual está trabalhando: basta conhecer a funcionalida<strong>de</strong> do seu circuito.<br />

Figura 5.4: Parâmetros configuráveis via HTML, para geração da applet .<br />

Neste processo evi<strong>de</strong>nciam-se três atores: o <strong>de</strong>senvolvedor do software, o projetista do circuito, e<br />

o usuário do sistema.<br />

O <strong>de</strong>senvolvedor do programa vai implementar uma camada <strong>de</strong> software para escon<strong>de</strong>r <strong>de</strong>talhes<br />

arquiteturais do usuário do circuito e do projetista do hardware. O programador <strong>de</strong>ve conhecer o fun-<br />

cionamento das classes JBits - como acessar e alterar informações do bitstream, bem como o posici-<br />

onamento dos parâmetros a serem reconfigurados. Esta etapa realiza-se uma única vez, incorporando<br />

o conhecimento adquirido no <strong>de</strong>senvolvimento da ferramenta da seção 5.1.<br />

O projetista <strong>de</strong> hardware realiza seu projeto em VHDL conhecendo apenas o posicionamento dos<br />

elementos <strong>de</strong> memória. Então cria uma página html para possibilitar a reconfiguração do circuito.<br />

Para criar esta página ele <strong>de</strong>ve saber quais os parâmetros que o applet aceita. E é apenas isso - toda a<br />

parte <strong>de</strong> en<strong>de</strong>reçamento e arquitetura é abstraída. A Figura 5.5 mostra a página gerada.<br />

Já o usuário do circuito não precisa sequer saber em qual família <strong>de</strong> FPGAs seu sistema foi imple-<br />

mentado. Ou seja, não há necessida<strong>de</strong> que ele tenha noção nem <strong>de</strong> VHDL, nem <strong>de</strong> JBits. O usuário<br />

78