pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

B−1 bits<br />

para o<br />

proximo ´ EP<br />

Barramentos<br />

Globais<br />

2.5.3 RAW<br />

B<br />

Bits <strong>de</strong> carry e controle<br />

Saídas do estágio<br />

anterior<br />

Re<strong>de</strong> <strong>de</strong> Interconexão<br />

X Y<br />

Deslo−<br />

cador<br />

X Y<br />

Unida<strong>de</strong> Lógica<br />

e Aritmética<br />

Saída<br />

B<br />

Deslo−<br />

cador<br />

B<br />

Para a Re<strong>de</strong> <strong>de</strong> Interconexão<br />

Bits <strong>de</strong> carry e controle<br />

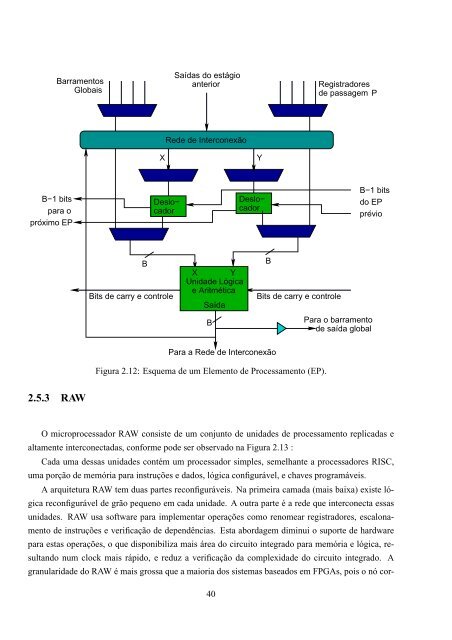

Figura 2.12: Esquema <strong>de</strong> um Elemento <strong>de</strong> Processamento (EP).<br />

Registradores<br />

<strong>de</strong> passagem P<br />

Para o barramento<br />

<strong>de</strong> saída global<br />

B−1 bits<br />

do EP<br />

previo ´<br />

O microprocessador RAW consiste <strong>de</strong> um conjunto <strong>de</strong> unida<strong>de</strong>s <strong>de</strong> processamento replicadas e<br />

altamente interconectadas, conforme po<strong>de</strong> ser observado na Figura 2.13 :<br />

Cada uma <strong>de</strong>ssas unida<strong>de</strong>s contém um processador simples, semelhante a processadores RISC,<br />

uma porção <strong>de</strong> memória para instruções e dados, lógica configurável, e chaves programáveis.<br />

A arquitetura RAW tem duas partes reconfiguráveis. Na primeira camada (mais baixa) existe ló-<br />

gica reconfigurável <strong>de</strong> grão pequeno em cada unida<strong>de</strong>. A outra parte é a re<strong>de</strong> que interconecta essas<br />

unida<strong>de</strong>s. RAW usa software para implementar operações como renomear registradores, escalona-<br />

mento <strong>de</strong> instruções e verificação <strong>de</strong> <strong>de</strong>pendências. Esta abordagem diminui o suporte <strong>de</strong> hardware<br />

para estas operações, o que disponibiliza mais área do circuito integrado para memória e lógica, re-<br />

sultando num clock mais rápido, e reduz a verificação da complexida<strong>de</strong> do circuito integrado. A<br />

granularida<strong>de</strong> do RAW é mais grossa que a maioria dos sistemas baseados em FPGAs, pois o nó cor-<br />

40