pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

4.1 Atmel<br />

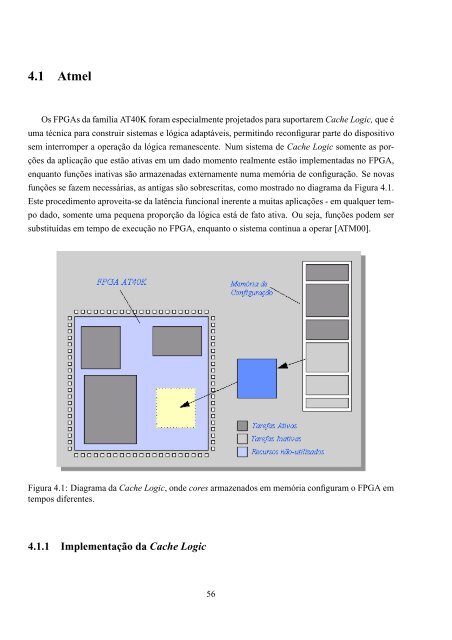

Os FPGAs da família AT40K foram especialmente projetados para suportarem Cache Logic, que é<br />

uma técnica para construir sistemas e lógica adaptáveis, permitindo reconfigurar parte do dispositivo<br />

sem interromper a operação da lógica remanescente. Num sistema <strong>de</strong> Cache Logic somente as por-<br />

ções da aplicação que estão ativas em um dado momento realmente estão implementadas no FPGA,<br />

enquanto funções inativas são armazenadas externamente numa memória <strong>de</strong> configuração. Se novas<br />

funções se fazem necessárias, as antigas são sobrescritas, como mostrado no diagrama da Figura 4.1.<br />

Este procedimento aproveita-se da latência funcional inerente a muitas aplicações - em qualquer tem-<br />

po dado, somente uma pequena proporção da lógica está <strong>de</strong> fato ativa. Ou seja, funções po<strong>de</strong>m ser<br />

substituídas em tempo <strong>de</strong> execução no FPGA, enquanto o sistema continua a operar [ATM00].<br />

Figura 4.1: Diagrama da Cache Logic, on<strong>de</strong> cores armazenados em memória configuram o FPGA em<br />

tempos diferentes.<br />

4.1.1 Implementação da Cache Logic<br />

56