pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

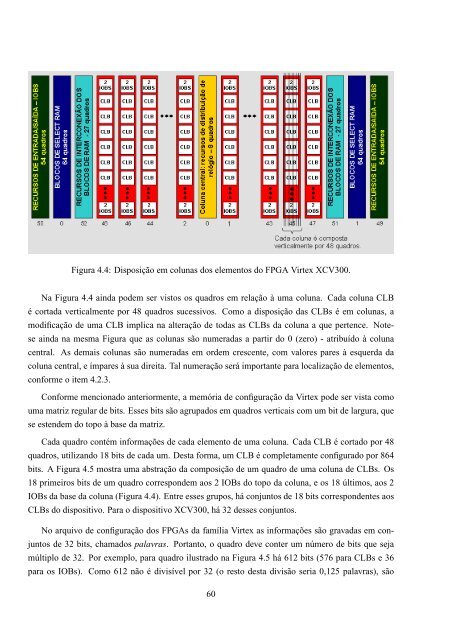

Figura 4.4: Disposição em colunas dos elementos do FPGA Virtex XCV300.<br />

Na Figura 4.4 ainda po<strong>de</strong>m ser vistos os quadros em relação à uma coluna. Cada coluna CLB<br />

é cortada verticalmente por 48 quadros sucessivos. Como a disposição das CLBs é em colunas, a<br />

modificação <strong>de</strong> uma CLB implica na alteração <strong>de</strong> todas as CLBs da coluna a que pertence. Note-<br />

se ainda na mesma Figura que as colunas são numeradas a partir do 0 (zero) - atribuído à coluna<br />

central. As <strong>de</strong>mais colunas são numeradas em or<strong>de</strong>m crescente, com valores pares à esquerda da<br />

coluna central, e ímpares à sua direita. Tal numeração será importante para localização <strong>de</strong> elementos,<br />

conforme o item 4.2.3.<br />

Conforme mencionado anteriormente, a memória <strong>de</strong> configuração da Virtex po<strong>de</strong> ser vista como<br />

uma matriz regular <strong>de</strong> bits. Esses bits são agrupados em quadros verticais com um bit <strong>de</strong> largura, que<br />

se esten<strong>de</strong>m do topo à base da matriz.<br />

Cada quadro contém informações <strong>de</strong> cada elemento <strong>de</strong> uma coluna. Cada CLB é cortado por 48<br />

quadros, utilizando 18 bits <strong>de</strong> cada um. Desta forma, um CLB é completamente configurado por 864<br />

bits. A Figura 4.5 mostra uma abstração da composição <strong>de</strong> um quadro <strong>de</strong> uma coluna <strong>de</strong> CLBs. Os<br />

18 primeiros bits <strong>de</strong> um quadro correspon<strong>de</strong>m aos 2 IOBs do topo da coluna, e os 18 últimos, aos 2<br />

IOBs da base da coluna (Figura 4.4). Entre esses grupos, há conjuntos <strong>de</strong> 18 bits correspon<strong>de</strong>ntes aos<br />

CLBs do dispositivo. Para o dispositivo XCV300, há 32 <strong>de</strong>sses conjuntos.<br />

No arquivo <strong>de</strong> configuração dos FPGAs da família Virtex as informações são gravadas em con-<br />

juntos <strong>de</strong> 32 bits, chamados palavras. Portanto, o quadro <strong>de</strong>ve conter um número <strong>de</strong> bits que seja<br />

múltiplo <strong>de</strong> 32. Por exemplo, para quadro ilustrado na Figura 4.5 há 612 bits (576 para CLBs e 36<br />

para os IOBs). Como 612 não é divisível por 32 (o resto <strong>de</strong>sta divisão seria 0,125 palavras), são<br />

60